# TOMÁS RODRIGUES LUCAS AMARO GONÇALVES

Licenciado em Ciências da Engenharia Eletrotécnica e de Computadores

# MULTIPLICAÇÃO DE INTEIROS EM HARDWARE DIGITAL

IMPLEMENTAÇÃO EM VHDL

MESTRADO EM ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

## DEPARTAMENTO DE ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

# MULTIPLICAÇÃO DE INTEIROS EM HARDWARE DIGITAL IMPLEMENTAÇÃO EM VHDL

# TOMÁS RODRIGUES LUCAS AMARO GONÇALVES

Licenciado em Ciências da Engenharia Eletrotécnica e de Computadores

Orientador: Luís Filipe dos Santos Gomes

Professor Associado com Agregação, FCT-NOVA

Júri

Presidente: Filipa Alexandra Moreira Ferrada, Professora Auxiliar, FCT-NOVA

Arguente: Anikó Katalin da Costa, Professora Auxiliar, FCT-NOVA

Luís Filipe dos Santos Gomes, Professor Associado com

Orientador: Agregação, FCT-NOVA

### Multiplicação de inteiros em hardware digital Implementação em VHDL

Copyright © Tomás Rodrigues Lucas Amaro Gonçalves, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

Este documento foi gerado com o processador LATEX e o modelo NOVAthesis (v7.0.1) [1].

# AGRADECIMENTOS

Primeiramente, agradeço ao Professor Luís Gomes, pelo apoio desde o início e ao longo de todo o processo de dissertação e pela disponibilidade constante para me orientar. Como Professor, mostrou-me que a relação dos professores com os alunos vai para além da formação académica, de uma forma muito humana.

Agradeço, de um modo geral, a todos os Professores que me acompanharam na Faculdade, pelo apoio neste caminho que é a nossa formação. E aos colegas com quem me cruzei e que daí ficaram amizades para além do curso. Neste curso e na FCT NOVA aprendese a arte da Engenharia mas também aprende-se a trabalhar com pessoas. Costumava dizer-se que o curso não se faz sozinho. Mas a vida profissional é exatamente a mesma coisa. É necessário haver uma constante entreajuda em qualquer ambiente de trabalho, seja num espaço académico ou outro. Os Professores e os colegas contribuíram para o meu desenvolvimento pessoal em cooperação e com uma abrangência humanística.

Por fim, agradeço à minha família pelo constante apoio nesta grande viagem que foi o Curso.

# Resumo

A operação de multiplicação está presente na generalidade dos sistemas de computação envolvendo operações aritméticas. Assim, é relevante para a construção de qualquer circuito identificar os métodos mais eficientes de implementação da operação de multiplicação de inteiros. Baseando-se na análise de soluções para a realização de multiplicadores de números inteiros em hardware, o objetivo principal desta dissertação é o de analisar soluções que permitem o seu cálculo durante um ciclo de relógio, bem como gerar código VHDL associado à sua implementação. Assim, são analisadas diferentes arquiteturas de multiplicação de inteiros, nomeadamente os multiplicadores de matriz, de Booth e de Wallace. É explorada também a utilização de tabelas de consulta (Look-Up Tables), de forma a obter soluções de implementação aproximadas. A solução aproximada consistirá na utilização de espaços transformados, utilizando logaritmos, guardados em tabelas de consulta, sendo incluída uma análise da relação entre o erro do resultante no cálculo do produto e o número de bits dos operandos e das tabelas de consulta. Após a análise, as topologias referidas são implementadas utilizando a linguagem VHDL. Assim, para cada método, é apresentada a sua implementação em VHDL, com o devido estudo prévio sobre a sua arquitetura. Finalmente, tendo o referido objetivo de gerar código VHDL de multiplicadores de solução de lógica combinatória, esta dissertação contribui com a criação de uma ferramenta, em Python, para gerar automaticamente o código VHDL para a multiplicação em lógica combinatória.

**Palavras-chave:** VHDL, Python, Multiplicador de matriz, Multiplicador de Wallace, Multiplicador de Booth, Tabelas de consulta

# ABSTRACT

Multiplication is present in almost all computing systems including arithmetic operations. It is therefore important for the construction of any circuit to identify the most efficient methods of implementing the multiplication of integer numbers. Based on the analysis of solutions for the implementation of multipliers of integers in hardware, the main objective of this dissertation is to analyze solutions that allow their calculation during a clock cycle, as well as to generate VHDL code associated with their implementation. Different integer multiplication architectures are analysed, namely Array Multiplier, Booth's Multiplier and Wallace Tree Multiplier. The use of look-up tables is also explored in order to obtain algorithms of approximate results. The approximate results will be obtained by using transformation functions using logarithms, saved in look-up tables. It will also be analysed the relation between the resulting error after the multiplication process and the number of bits of the operands and look-up tables. After the analysis, the previous topologies are implemented using VHDL language code. Thus, for each method, its implementation in VHDL is presented, with the appropriate analysis of its architecture. Finally, with the aim of generating VHDL code for combinational logic multipliers, this dissertation contributes with the implementation of an algorithm, in Python, to automatically generate the VHDL code for combinational multipliers.

**Keywords:** VHDL, Python, Array Multiplier, Wallace Tree Multiplier, Booth's Multiplier, Look-Up Tables

# Índice

| Ín | dice         | de Figu | ıras                                                     | xiii |  |  |

|----|--------------|---------|----------------------------------------------------------|------|--|--|

| Ín | dice         | de Tabe | elas                                                     | xvii |  |  |

| 1  | 1 Introdução |         |                                                          |      |  |  |

|    | 1.1          | Motiv   | ração e Contexto                                         | 1    |  |  |

|    | 1.2          | Objeti  | ivos da Dissertação                                      | 2    |  |  |

|    | 1.3          | Estrut  | tura da Dissertação                                      | 3    |  |  |

| 2  | Esta         | do de A | Arte                                                     | 5    |  |  |

|    | 2.1          | Introd  | lução                                                    | 5    |  |  |

|    |              | 2.1.1   | Apresentação de soluções baseadas em lógica combinatória | 5    |  |  |

|    | 2.2          | Algor   | itmos Exatos                                             | 6    |  |  |

|    |              | 2.2.1   | Somas sucessivas                                         | 6    |  |  |

|    |              | 2.2.2   | Soma e deslocamento                                      | 6    |  |  |

|    |              | 2.2.3   | Multiplicador de matriz (Multiplicador de array)         | 8    |  |  |

|    |              | 2.2.4   | Algoritmo de Booth                                       | 9    |  |  |

|    |              | 2.2.5   | Algoritmo de Wallace                                     | 11   |  |  |

|    |              | 2.2.6   | Gestão do transporte durante a operação                  | 12   |  |  |

|    | 2.3          | Algor   | itmos Aproximados                                        | 15   |  |  |

|    |              | 2.3.1   | Tabelas de consulta (Look-Up Tables)                     | 15   |  |  |

|    |              | 2.3.2   | Espaços Transformados - Logaritmos                       | 16   |  |  |

| 3  | Aná          | lise de | soluções exatas                                          | 17   |  |  |

|    | 3.1          | Conce   | eção de cada circuito                                    | 17   |  |  |

|    |              | 3.1.1   | Multiplicador de matriz                                  | 18   |  |  |

|    |              | 3.1.2   | Multiplicador de Wallace                                 | 23   |  |  |

|    |              | 3.1.3   | Multiplicador de Booth                                   | 28   |  |  |

|    | 3.2          | Consi   | derações sobre tempos de propagação                      | 29   |  |  |

|    |       | 3.2.1   | Tempo de processamento dos métodos do transporte guardado e da propagação do transporte | 29 |

|----|-------|---------|-----------------------------------------------------------------------------------------|----|

|    |       | 3.2.2   | Análise de duas variantes de multiplicador de matriz com propaga-                       |    |

|    |       |         | ção de transporte                                                                       | 30 |

| 4  | Aná   | lise de | soluções aproximadas                                                                    | 33 |

|    | 4.1   | Tabela  | s de consulta (Look-Up Tables)                                                          | 33 |

|    | 4.2   | Arquit  | tetura e fluxograma de uma solução aproximada utilizando tabelas                        |    |

|    |       | de con  | sulta (Look-Up Table)                                                                   | 34 |

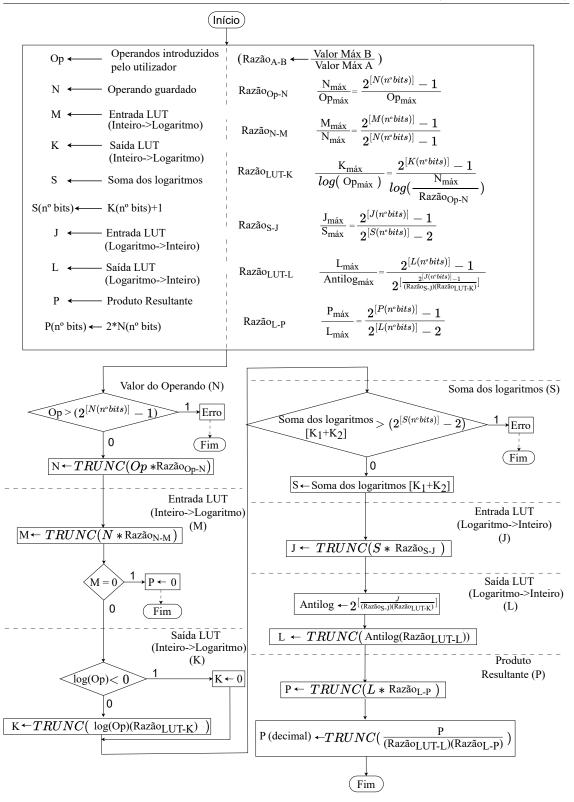

|    |       | 4.2.1   | Inicialização                                                                           | 36 |

|    |       | 4.2.2   | Valor do Operando                                                                       | 37 |

|    |       | 4.2.3   | Entrada Look-Up Table (Inteiro-Logaritmo)                                               | 38 |

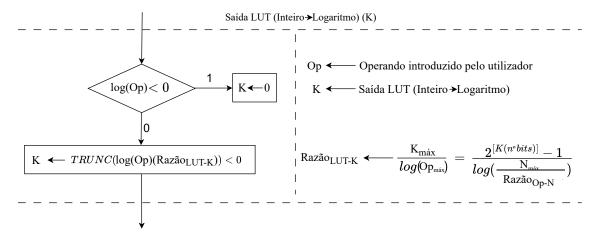

|    |       | 4.2.4   | Saída Look-Up Table (Inteiro-Logaritmo)                                                 | 39 |

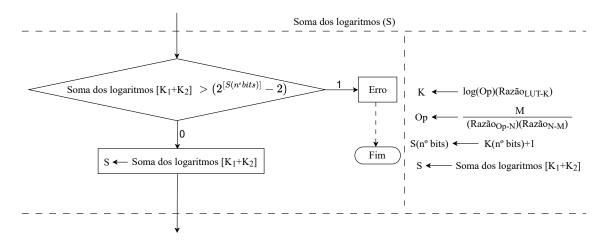

|    |       | 4.2.5   | Soma dos logaritmos                                                                     | 39 |

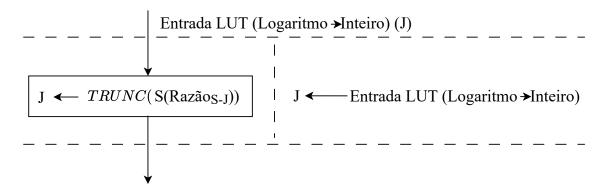

|    |       | 4.2.6   | Entrada Look-Up Table (Logaritmo-Inteiro)                                               | 40 |

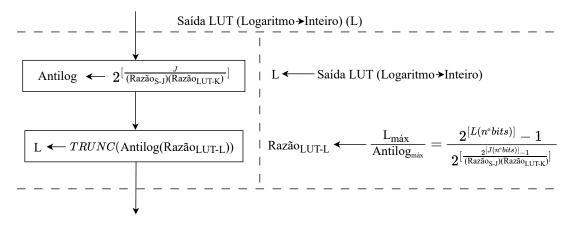

|    |       | 4.2.7   | Saída Look-Up Table (Logaritmo-Inteiro)                                                 | 40 |

|    |       | 4.2.8   | Produto Resultante                                                                      | 41 |

|    | 4.3   | Result  | ados obtidos sobre o erro de uma solução aproximada                                     | 41 |

| 5  | Con   | clusões | <b>3</b>                                                                                | 49 |

|    | 5.1   | Trabal  | ho Futuro                                                                               | 49 |

| Bi | bliog | rafia   |                                                                                         | 51 |

| A  | nexos |         |                                                                                         |    |

| I  | Ane   | xo      |                                                                                         | 56 |

|    | I.1   | Códig   | o em Python para gerar código VHDL para o multiplicador de matriz                       |    |

|    |       | atravé  | s de propagação de transporte, com 4 bits em cada operando                              | 56 |

|    | I.2   | Códig   | o VHDL gerado para o multiplicador de matriz através de propagação                      |    |

|    |       |         | nsporte, com 4 bits em cada operando                                                    | 63 |

|    | I.3   | _       | o em Python para gerar código VHDL para o multiplicador de matriz                       |    |

|    |       |         | s de transporte guardado, com 4 bits em cada operando                                   | 67 |

|    | I.4   | _       | o VHDL gerado para o multiplicador de matriz através de transporte                      |    |

|    |       |         | ado, com 4 bits em cada operando                                                        | 76 |

|    | I.5   | _       | o VHDL para o multiplicador de Wallace, utilizando o método 2-4-2,                      |    |

|    |       |         | bits em cada operando                                                                   | 81 |

|    | I.6   | -       | o VHDL para o multiplicador de Wallace, utilizando o método 3-0-1,                      | 0= |

|    | T 77  |         | bits em cada operando                                                                   | 87 |

|    | I.7   |         | o VHDL para o multiplicador de Wallace, utilizando o método 2-1-1,                      | 00 |

|    |       | com 4   | bits em cada operando                                                                   | 92 |

| I.8 | Código VHDL para o multiplicador de Wallace, utilizando o método 2-1-5, |     |

|-----|-------------------------------------------------------------------------|-----|

|     | com 4 bits em cada operando                                             | 98  |

| I.9 | Código VHDL para o multiplicador de Booth, com 4 bits em cada operando  | 104 |

# Índice de Figuras

| 2.1  | Exemplo de multiplicação de 4 bits por 4 bits                                 | 6  |

|------|-------------------------------------------------------------------------------|----|

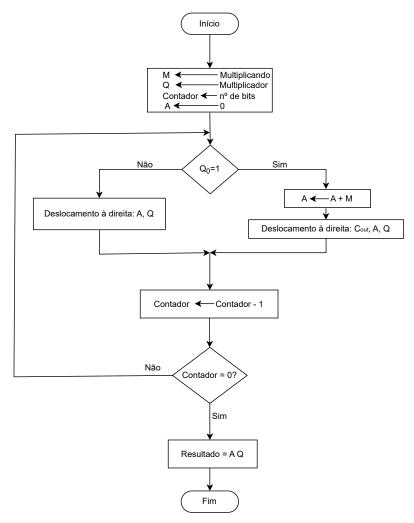

| 2.2  | Fluxograma do Algoritmo por soma e deslocamento                               | 7  |

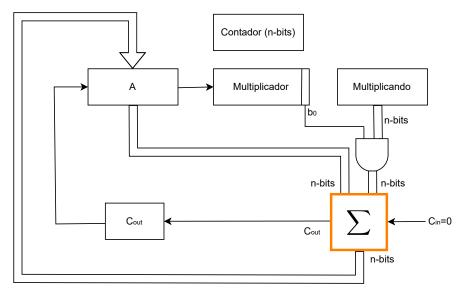

| 2.3  | Arquitetura do Algoritmo por soma e deslocamento                              | 7  |

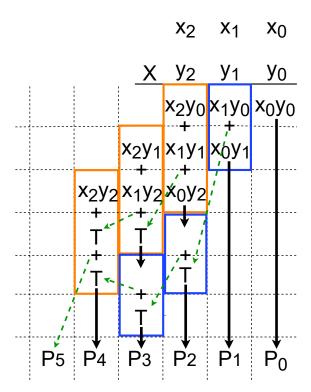

| 2.4  | Arquitetura do Multiplicador de matriz para 3 bits                            | 8  |

| 2.5  | Cálculos para 3 bits, com o Multiplicador de matriz, utilizando o método de   |    |

|      | propagação de transporte                                                      | 9  |

| 2.6  | Fluxograma do Algoritmo de Booth                                              | 10 |

| 2.7  | Exemplo de fase de codificação para o Algoritmo de Booth                      | 11 |

| 2.8  | Arquitetura do Algoritmo de Wallace de 4 bits                                 | 12 |

| 2.9  | Arquitetura para multiplicação de matriz através do Transporte Guardado,      |    |

|      | com 3 bits                                                                    | 13 |

| 2.10 | Cálculos para multiplicação com 3 bits, utilizando o Algoritmo com Transporte |    |

|      | Guardado                                                                      | 14 |

| 2.11 | Representação de uma tabela de consulta (Look-Up Table)                       | 15 |

| 2.12 | Representação do espaço transformado, utilizando logaritmos                   | 16 |

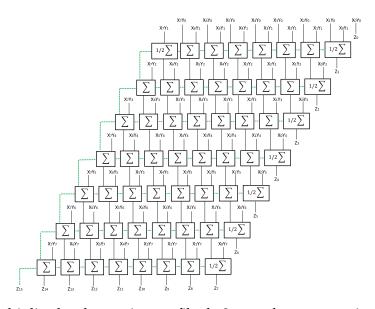

| 3.1  | Multiplicador de matriz                                                       | 18 |

| 3.2  | Estrutura de blocos para a multiplicação de matriz através de propagação de   |    |

|      | transporte                                                                    | 18 |

| 3.3  | Segmentação de colunas de somadores e semi-somadores, para a multiplicação    |    |

|      | de matriz através de propagação de transporte                                 | 19 |

| 3.4  | Processo de geração de código VHDL e a sua implementação numa FPGA .          | 19 |

| 3.5  | Extrato do código em Python para gerar código VHDL para a multiplicação       |    |

|      | de matriz através de propagação de transporte                                 | 20 |

| 3.6  | Extrato do código VHDL, gerado automaticamente, para a multiplicação de       |    |

|      | matriz através de propagação de transporte, com 2 bits em cada operando .     | 20 |

| 3.7  | Exemplo de um somador implementado em código VHDL, para a multiplicação       |    |

|      | de matriz através de propagação de transporte                                 | 21 |

| 3.8  | Estrutura de blocos para a multiplicação de matriz através do transporte                                            |            |

|------|---------------------------------------------------------------------------------------------------------------------|------------|

|      | guardado                                                                                                            | 22         |

| 3.9  | Segmentação de colunas de somadores e semi-somadores, para a multiplicação de matriz através do transporte guardado | 22         |

| 3.10 | Extrato do código em Python para gerar código VHDL para a multiplicação                                             |            |

|      | de matriz através do transporte guardado                                                                            | 22         |

| 3.11 | Extrato do código VHDL, gerado automaticamente, para a multiplicação de                                             |            |

|      | matriz através do transporte guardado, com 2 bits em cada operando                                                  | 23         |

| 3 12 | Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-4-2                                      | 24         |

|      | Extrato do código VHDL para o multiplicador de Wallace, utilizando o método                                         | <b>4</b> 1 |

| 0.10 | 2-4-2                                                                                                               | 24         |

| 2 11 |                                                                                                                     | 25         |

|      | Estrutura de blocos para o multiplicador de Wallace, utilizando o método 3-0-1                                      | 23         |

| 3.15 | Extrato do código VHDL para o multiplicador de Wallace, utilizando o método                                         | 25         |

|      | 3-0-1                                                                                                               | 25         |

| 3.16 | Cálculos para determinar a arquitetura do multiplicador de Wallace utilizando                                       |            |

|      | o método 2-1-1                                                                                                      | 26         |

|      | Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-1-1                                      | 26         |

| 3.18 | Extrato do código VHDL para o multiplicador de Wallace, utilizando o método                                         |            |

|      | 2-1-1                                                                                                               | 27         |

| 3.19 | Cálculos para determinar a arquitetura do multiplicador de Wallace utilizando                                       |            |

|      | o método 2-1-5                                                                                                      | 27         |

| 3.20 | Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-1-5                                      | 27         |

| 3.21 | Extrato do código VHDL para o multiplicador de Wallace, utilizando o método                                         |            |

|      | 2-1-5                                                                                                               | 28         |

| 3.22 | Arquitetura de soma e deslocamento e multiplicador de Booth                                                         | 28         |

| 3.23 | Extrato do código VHDL para o multiplicador de Booth                                                                | 29         |

|      | Comparação entre o método com transporte guardado e o método com propa-                                             |            |

|      | gação de transporte                                                                                                 | 30         |

| 3.25 | Multiplicador de matriz com fila de 7 somadores ou semi-somadores, utilizando                                       |            |

|      | propagação de transporte                                                                                            | 31         |

| 3.26 | Multiplicador de matriz com fila de 8 somadores ou semi-somadores, utilizando                                       | 01         |

| 0.20 | propagação de transporte                                                                                            | 31         |

| 3 27 | Caminhos críticos de um multiplicador de matriz com filas de 7 e 8 somadores                                        | 01         |

| 0.27 | ou semi-somadores, utilizando propagação de transporte                                                              | 32         |

|      | ou semi somadores, utilizando propagação de transporte                                                              | 32         |

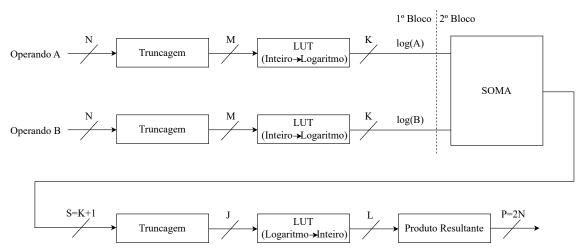

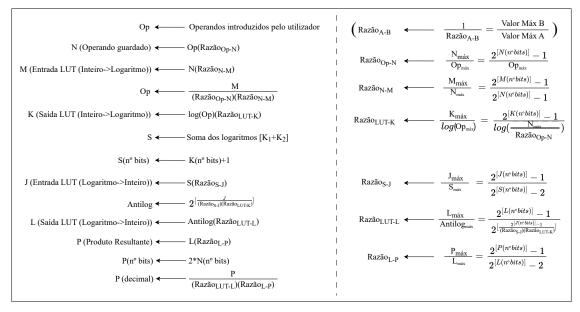

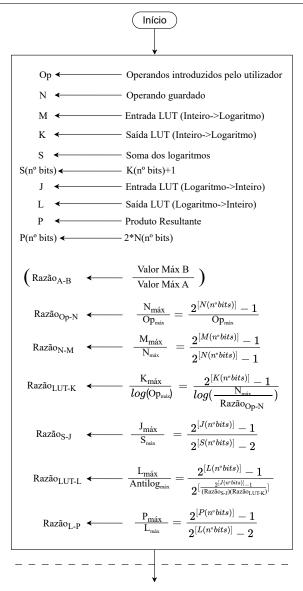

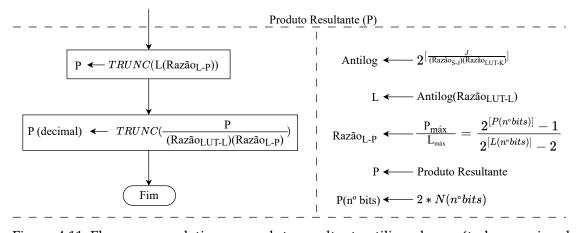

| 4.1  | Arquitetura de uma solução aproximada utilizando tabelas de consulta (Look-                                         |            |

|      | Up Table)                                                                                                           | 34         |

| 4.2  | Fluxograma de uma solução aproximada utilizando tabelas de consulta (Look-                                          |            |

|      | Up Table)                                                                                                           | 35         |

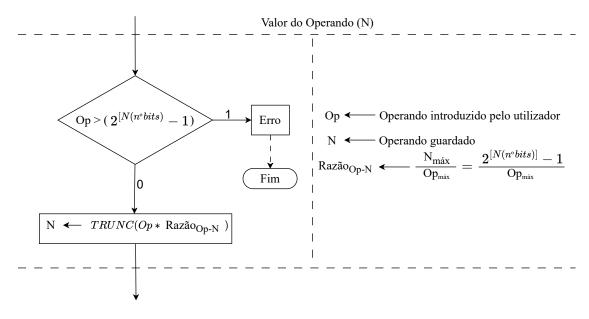

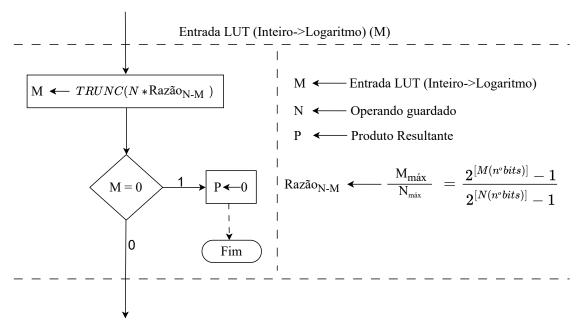

| 4.3  | Cálculos necessários para a obtenção dos valores em cada passo de execução                                          |            |

|      | do método aproximado utilizando tabelas de consulta (Look-Up Table)                                                 | 36         |

| 4.4  | Inicialização utilizando o método aproximado                                      | 37 |

|------|-----------------------------------------------------------------------------------|----|

| 4.5  | Fluxograma relativo ao valor do operando utilizando o método aproximado           | 38 |

| 4.6  | Fluxograma relativo à entrada da primeira tabela de consulta (Look-Up Table)      |    |

|      | utilizando o método aproximado                                                    | 38 |

| 4.7  | Fluxograma relativo à saída da primeira tabela de consulta (Look-Up Table)        |    |

|      | utilizando o método aproximado                                                    | 39 |

| 4.8  | Fluxograma relativo à soma dos logaritmos utilizando o método aproximado          | 40 |

| 4.9  | Fluxograma relativo à entrada da segunda tabela de consulta (Look-Up Table)       |    |

|      | utilizando o método aproximado                                                    | 40 |

| 4.10 | Fluxograma relativo à saída da segunda tabela de consulta (Look-Up Table)         |    |

|      | utilizando o método aproximado                                                    | 41 |

| 4.11 | Fluxograma relativo ao produto resultante utilizando o método aproximado          | 41 |

| 4.12 | Simulação sobre o primeiro bloco, que recebe na entrada os valores do operando    |    |

|      | (N) e devolve os valores logarítmicos (K)                                         | 42 |

| 4.13 | Simulação sobre o segundo bloco, que recebe na entrada a soma dos valores         |    |

|      | logarítmicos (S) e devolve o produto resultante (P)                               | 42 |

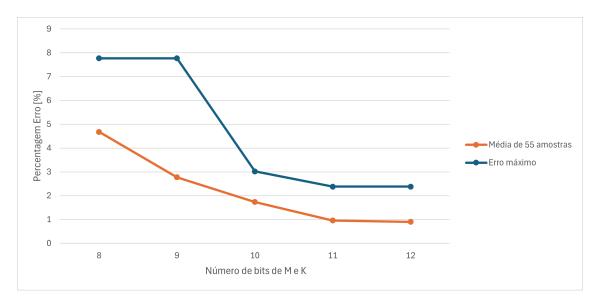

| 4.14 | Gráfico do erro calculado para $N$ com valor constante e $M$ e $K$ crescentes, de |    |

|      | acordo com a figura 4.1                                                           | 44 |

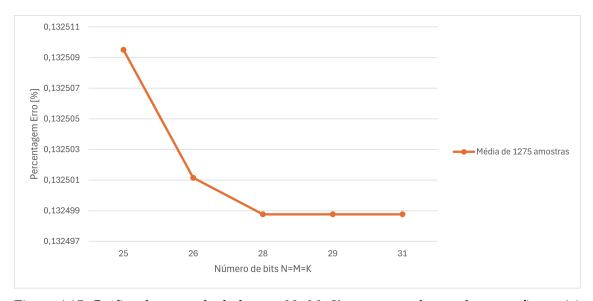

| 4.15 | Gráfico do erro calculado com $N=M=K$ crescentes, de acordo com a figura 4.1      | 45 |

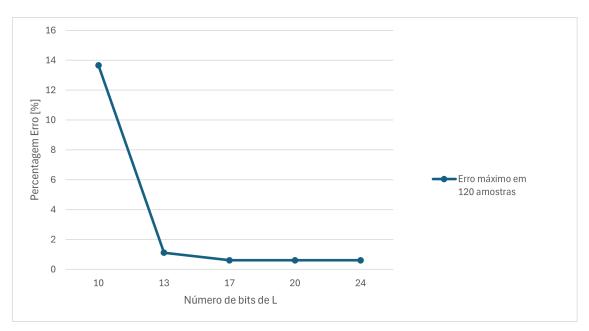

| 4.16 | Erro calculado com variação do número de bits em todos os componentes, de         |    |

|      | acordo com a figura 4.1                                                           | 45 |

| 4.17 | Gráfico do erro calculado com variação do número de bits em todos os compo-       |    |

|      | nentes, de acordo com a figura 4.1                                                | 46 |

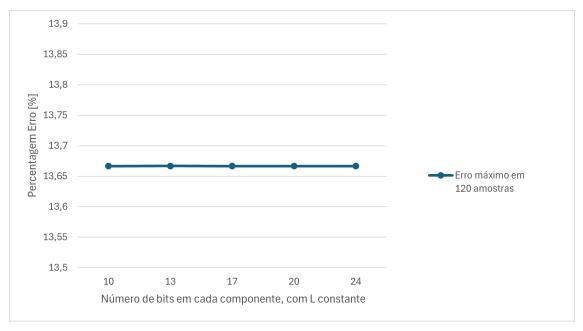

| 4.18 | Erro calculado com variação do número de bits em cada componente, com ${\cal L}$  |    |

|      | constante, de acordo com a figura 4.1                                             | 46 |

| 4.19 | Gráfico do erro calculado com variação do número de bits em cada componente,      |    |

|      | com $L$ constante, de acordo com a figura $4.1 \ldots \ldots \ldots \ldots$       | 47 |

# Índice de Tabelas

| 2.1 | Tabela de codificação para o Algoritmo de Booth                                                                   | 11 |

|-----|-------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Características das duas arquiteturas possíveis de um multiplicador de matriz utilizando propagação de transporte | 32 |

| 4.1 | Erro calculado para o número de bits $N$ com valor constante e $M$ e $K$ crescentes,                              |    |

|     | de acordo com a figura 4.1                                                                                        | 43 |

| 4.2 | Erro calculado com $N=M=K$ crescentes, de acordo com a figura 4.1                                                 | 44 |

# Introdução

## 1.1 Motivação e Contexto

Sendo a multiplicação uma operação matemática fundamental em sistemas digitais, esta está presente em diversas aplicações, de simples processadores a sistemas de redes neuronais. Nestas aplicações, os multiplicadores são essenciais para o bom funcionamento do circuito, mostrando-se relevantes para a máxima utilização da potência e para uma maior velocidade de processamento [2]. Ademais, o rápido crescimento do mercado de dispositivos eletrónicos portáteis com potência e área limitadas abriu um vasto leque de oportunidades de conceção de circuitos de baixo consumo e compactos, e de desafios na conceção de circuitos de integração em muito grande escala [3]. Os telemóveis são um dos exemplos de produtos eletrónicos portáteis que se tornaram parte integrante da vida quotidiana. Por conseguinte, o consumo de energia em circuitos integrados tem merecido especial atenção devido à proliferação de dispositivos eletrónicos de elevado desempenho. Uma vez que a multiplicação domina o tempo de execução da maioria dos algoritmos em circuitos integrados, é bastante desejável dispor de um multiplicador de alta velocidade. Por outro lado, a multiplicação continua a ser o fator dominante na determinação do tempo do ciclo de instruções de um circuito integrado [4].

O processo de multiplicação dependerá do tipo de representação dos valores dos operandos. Podem-se considerar operandos de números inteiros, positivos ou negativos, ou de números fracionários, que poderão ser representados por vírgula fixa ou por vírgula flutuante. O processo utilizando vírgula fixa é semelhante à representação de números inteiros, mas com uma convenção sobre onde está a vírgula. A vantagem é a facilidade de implementação, no entanto, tem um intervalo limitado de valores possíveis. Com vírgula flutuante, o valor do operando é representado pela mantissa e expoente, com o expoente a definir a sua ordem de grandeza. Relativamente ao método de vírgula fixa, a vírgula flutuante abrange um maior conjunto de valores. Nas suas aplicações em multiplicação, tanto a operação com vírgula fixa como a operação com vírgula flutuante, baseiam-se na multiplicação das bases e na soma dos expoentes.

Existe, assim, um conjunto de estratégias diferentes para realizar as operações de multiplicação. E estas irão diferir pela sua complexidade, pela área do circuito, pela velocidade de processamento e pela capacidade de memória. Por sua vez, a escolha da arquitetura a utilizar, dependerá do que se pretende implementar. Uma das formas de otimizar o desempenho do circuito passa pelo cálculo do transporte e pelas diferentes estratégias de o gerir. Se o foco for colocar toda a operação de multiplicação num só ciclo de relógio pode-se utilizar a lógica combinatória. Também existem soluções aproximadas, se se admitir uma margem de erro no produto final, de modo a proporcionar uma maior rapidez na obtenção dos resultados. Neste trabalho serão abordadas todas estas ferramentas referidas, no contexto da linguagem VHDL.

### 1.2 Objetivos da Dissertação

O objetivo desta dissertação é o de analisar soluções que permitam a realização de multiplicadores de números inteiros em hardware, considerando a sua execução num ciclo de relógio, bem como gerar código VHDL associado à sua implementação. Para isso, foram analisadas diferentes hipóteses de implementação da operação de multiplicação de valores inteiros positivos em VHDL. Assim, será realizado um levantamento de diferentes abordagens de implementação para depois caracterizar as várias soluções, nomeadamente, validar as mesmas relativamente ao desempenho, erro, recursos, e comparar com os restantes métodos.

Como referido, apenas a multiplicação de valores inteiros positivos será admitida para análise. Os resultados deverão ser categorizados como exatos e aproximados, e determinar, para os resultados aproximados, quais são as consequências. A avaliação destas consequências dependerá da dimensão dos valores a multiplicar, que terá associada uma certa percentagem de erro. Assim, será útil fazer uma análise dos erros máximos dos métodos aproximados. Essa percentagem poderá ser definida consoante as diferentes aplicações.

Com este trabalho será feita uma análise completa em torno das várias configurações possíveis em relação à complexidade dos circuitos utilizados, necessária para incorporar os multiplicadores num ambiente de co-design com Redes de Petri, presente na plataforma IOPT-Tools. Nesta interface, é possível descrever o comportamento de um sistema, baseado, por exemplo, no controlador FPGA, com uma representação dos eventos, e dos sinais de entrada e saída. Dentro da plataforma, e num ponto de vista de hardware, o passo de execução terá de ser feito num ciclo de relógio. Esta condição será um dos vários aspetos que se terá em conta, durante a análise das diferentes hipóteses de implementação. Assim, com este estudo será possível dar resposta ao desenvolvimento, não apenas da plataforma IOPT Tools, mas de outras ferramentas que envolvam a operação de multiplicação em linguagem VHDL.

## 1.3 Estrutura da Dissertação

Esta dissertação organiza-se por:

- Capítulo 2, Estado de Arte, apresenta os diferentes métodos de multiplicação. Dividindo-os em métodos de resultado exato e aproximado, apresenta-os com breves descrições das suas arquiteturas.

- Capítulo 3, Análise de soluções exatas, apresenta uma análise aprofundada sobre as tipologias de multiplicadores de solução exata, nomeadamente, multiplicadores de matriz, multiplicadores de Wallace e multiplicadores de Booth. Para cada método, é apresentada a sua implementação em VHDL. Para os multiplicadores que o permitem, devido à sua regularidade, é implementado um algoritmo, em Python, para gerar automaticamente o código VHDL, consoante o número de bits em cada operando.

- Capítulo 4, Análise de soluções aproximadas, apresenta um estudo sobre o erro admitido em diferentes configurações de solução aproximada, que consistirão na utilização de espaços transformados, através de logaritmos, guardados nas tabelas de consulta. As configurações variam através do número de bits ao longo do multiplicador e que, consequentemente, irá afetar o erro. Assim, são apresentados resultados sobre a relação entre o erro do produto resultante e a variação do número de bits dos operandos.

- Capítulo 5, Conclusões, apresenta um resumo do trabalho e da análise que foi realizada. Inclui também comentários sobre trabalho futuro que pode ser efetuado, nomeadamente de outras perspetivas de análise do desempenho dos multiplicadores.

- Anexo I, Anexo, apresenta os códigos VHDL e Python dos diferentes multiplicadores que foram implementados.

# Estado de Arte

#### 2.1 Introdução

Neste capítulo serão abordados vários algoritmos de multiplicação, presentes na literatura científica, que diferem pela sua complexidade.

Os métodos serão divididos em algoritmos que produzem o resultado exato e algoritmos que poderão obter um resultado aproximado, admitindo uma margem de erro no produto final, para permitir uma maior rapidez de processamento. Tanto as soluções aproximadas, através de tabelas de consulta (Look-Up tables) e espaços transformados, como as exatas, através de algoritmos como Booth, Wallace ou multiplicador de matriz, poderão ser obtidas por métodos sequenciais ou por lógica combinatória.

Tendo em vista uma futura implementação na plataforma IOPT-Tools, em *co-design*, entre *software* e *hardware*, o passo de execução terá de ser feito num ciclo de relógio. Desse modo, será de particular interesse considerar, para análise, estratégias envolvendo lógica combinatória.

#### 2.1.1 Apresentação de soluções baseadas em lógica combinatória

Os multiplicadores com lógica combinatória são vantajosos pela sua simplicidade e velocidade. Tendo em conta a ausência de elementos sequenciais, o seu passo de execução poderá ser incluído dentro de um ciclo de relógio. No entanto, poderão ser necessários circuitos adicionais, ou compensações relativamente a um maior consumo de energia e a uma maior área a ser utilizada [5].

A maioria dos métodos de multiplicação com lógica combinatória são baseados na forma como se fazem operações básicas de multiplicação com números decimais no papel [6]. Numa função combinatória, também é possível escrever uma tabela de verdade que represente o produto de 2n bits, resultado da multiplicação de duas variáveis de n [7].

Neste capítulo, serão apresentados alguns dos algoritmos mais comuns, que poderão ser implementados com lógica combinatória e que têm como função a multiplicação. Cada

um destes métodos tem as suas vantagens e desvantagens no processo de implementação, consoante o número de bits ou a aproximação ao resultado. Serão também identificadas diferentes estratégias de gerir o transporte durante a operação, com o objetivo da otimização dos recursos.

#### 2.2 Algoritmos Exatos

#### 2.2.1 Somas sucessivas

O algoritmo das somas sucessivas é um possível método para a operação de multiplicação. Consiste num somador, que soma o valor do multiplicador, e um contador, cujo número de ciclos equivale ao valor do multiplicando. A desvantagem desta estratégia é a possibilidade de um elevado tempo de execução, pois este irá estar diretamente relacionado com o valor correspondente ao multiplicador. É, portanto, um algoritmo pouco eficiente na sua implementação.

#### 2.2.2 Soma e deslocamento

Outro possível método para a multiplicação, mais comum, é o algoritmo da soma e deslocamento, representando a operação de multiplicação na sua forma básica. Como ilustrado na figura 2.1, as somas resultantes da análise de cada um dos bits do multiplicador, são realizadas em posições com pesos mais elevados, resultando no deslocamento de um bit sempre que um novo bit do multiplicador é analisado.

|       |   |   | 1 | 0 | 1 | 1 |

|-------|---|---|---|---|---|---|

|       | _ | Χ | 0 | 1 | 0 | 1 |

|       |   |   | 1 | 0 | 1 | 1 |

|       |   | 0 | 0 | 0 | 0 |   |

|       | 1 | 0 | 1 | 1 |   |   |

| <br>0 | 0 | 0 | 0 | r |   |   |

| 0     | 1 | 1 | 0 | 1 | 1 | 1 |

Figura 2.1: Exemplo de multiplicação de 4 bits por 4 bits

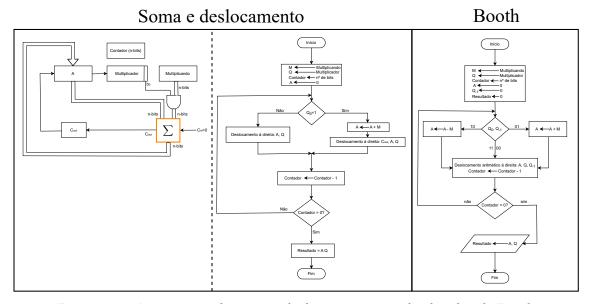

A vantagem deste algoritmo é o facto do tempo de execução não estar relacionado com o valor do multiplicador. Este algoritmo é determinístico, isto é, o período de execução depende, apenas, do número de bits dos operandos. Relativo à implementação, necessita apenas de um somador e um conjunto de registos. O seu fluxograma e arquitetura estão representados pelas figuras 2.2 e 2.3, respetivamente.

Figura 2.2: Fluxograma do Algoritmo por soma e deslocamento

Figura 2.3: Arquitetura do Algoritmo por soma e deslocamento

#### 2.2.3 Multiplicador de matriz (Multiplicador de array)

O multiplicador de matriz (multiplicador de array), para valores de pequenas dimensões, consiste num circuito simples, baseado em lógica combinatória. Contudo, enquanto o algoritmo de soma e deslocamento realiza a adição de dois números binários com um somador e guarda num registo, antes de deslocar o valor armazenado, numa operação de multiplicação de m.n bits, o multiplicador de matriz irá necessitar de (m-2).n somadores, n semi-somadores e m.n portas lógicas AND. Desta forma, o circuito do multiplicador de matriz será mais complexo do que o algoritmo da soma e deslocamento. O referido circuito é apresentado na figura 2.4.

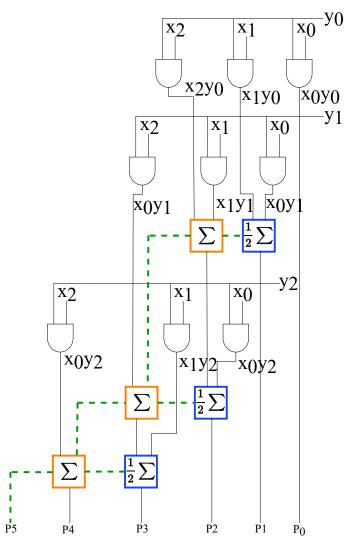

Figura 2.4: Arquitetura do Multiplicador de matriz para 3 bits

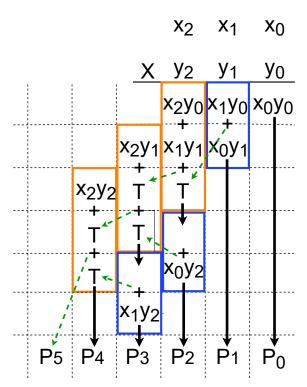

Figura 2.5: Cálculos para 3 bits, com o Multiplicador de matriz, utilizando o método de propagação de transporte

Assim, o multiplicador de matriz é organizado por várias fases de somadores e portas lógicas *AND*. Gera todos os produtos parciais após apenas um atraso de porta *AND*. De seguida, soma todos os produtos parciais. É possível observar o processo dos cálculos realizados na figura 2.5. A vantagem desta estrutura é que a disposição dos seus somadores é muito regular. No entanto, ocupa mais área e hardware do que o multiplicador iterativo. Este método irá conter o referido tempo de atraso, cujo valor acumulado será tanto maior quanto maior for o número de bits à entrada. Devido ao transporte, até o bit menos significativo poderá afetar o bit mais significativo.

Se se pretender integrar o multiplicador num determinado processamento, isso irá levar a um condicionamento do passo de execução porque a função do multiplicador terá que estabilizar dentro de um ciclo de relógio. Ou seja, irá limitar a frequência do sinal de relógio. No entanto, é vantajoso na medida em que será executado num ciclo, enquanto os períodos de execução dos algoritmos sequenciais irão demorar vários ciclos, apesar da sua frequência poder ser superior [8].

#### 2.2.4 Algoritmo de Booth

Em 1951, Andrew Booth desenhou um algoritmo que permite multiplicar números de grande dimensão, positivos ou negativos [9]. Este efetua a multiplicação gerando produtos parciais. Desloca para a direita um bit do multiplicador e do produto após cada cálculo de produto parcial. O produto parcial de um estado é definido como a soma, ou a subtração,

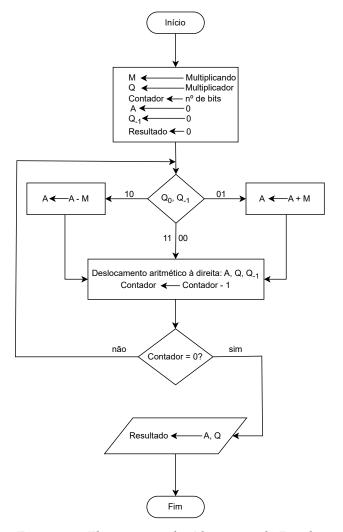

dependendo do estado anterior e atual do bit do multiplicador, entre o produto parcial anterior e o multiplicando do estado atual. Este processo está representado através de um fluxograma, na figura 2.6.

Figura 2.6: Fluxograma do Algoritmo de Booth

Desta forma, o algoritmo de Booth permite simplificar uma multiplicação transformando valores de grandes dimensões, positivos ou negativos, em sequências de bits de valor unitário. Esta simplificação é devida à verificação do estado anterior e o estado atual. Se ambos os estados conterem o mesmo valor, evita-se qualquer operação aritmética, apenas é feito o deslocamento. Assim, comparando com o método de soma e deslocamento convencional, o método de Booth reduz eficazmente o número de cálculos auxiliares [10].

#### 2.2.4.1 Algoritmo de Booth com codificação

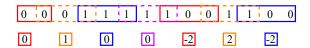

É possível modificar o algoritmo de Booth e acrescentar fases de codificação e descodificação, utilizando a conversão presente na tabela 2.1. Esta conversão permite reduzir o número de produtos parciais, como exemplificado na figura 2.7. O uso de um algoritmo de

codificação de Booth poderá evitar a criação de vários produtos parciais e reduzir o tempo de processamento, com um acrescento de complexidade ao circuito. A complexidade da operação poderá aumentar devido à presença de vários múltiplos dificilmente obtidos através de potências de 2, ao utilizar uma base numérica elevada para a codificação.

Figura 2.7: Exemplo de fase de codificação para o Algoritmo de Booth

| b <sub>i+1</sub> | b <sub>i</sub> | b <sub>i-1</sub> | valor |

|------------------|----------------|------------------|-------|

| 0                | 0              | 0                | 0     |

| 0                | 0              | 1                | 1     |

| 0                | 1              | 0                | 1     |

| 0                | 1              | 1                | 2     |

| 1                | 0              | 0                | -2    |

| 1                | 0              | 1                | -1    |

| 1                | 1              | 0                | -1    |

| 1                | 1              | 1                | 0     |

Tabela 2.1: Tabela de codificação para o Algoritmo de Booth

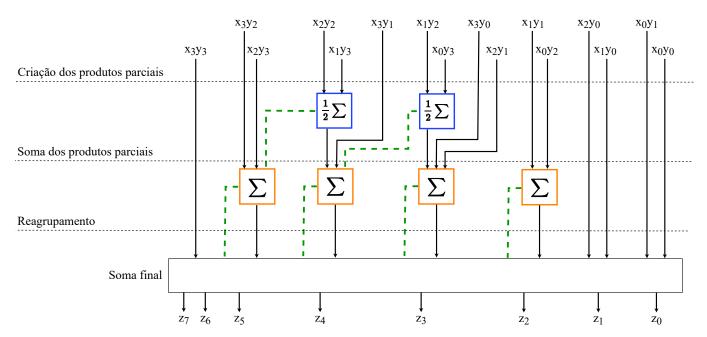

#### 2.2.5 Algoritmo de Wallace

O algoritmo de Wallace baseia-se numa estrutura em forma de árvore, onde utiliza somadores para reduzir a quantidade de produtos parciais [11]. Este método possibilita multiplicar dois valores inteiros de grandes dimensões de uma forma mais rápida do que o método por soma e deslocamento, porém com o mesmo número de deslocamentos, pois para uma multiplicação de n.n bits existem  $n^2$  produtos parciais a serem somados. O método de Wallace consiste em três fases [12]:

- Criação dos produtos parciais;

- Soma dos produtos parciais e reagrupamento;

- · Soma final.

Figura 2.8: Arquitetura do Algoritmo de Wallace de 4 bits

Um exemplo de multiplicação de 4 bits é apresentado na figura 2.8. Na criação dos produtos parciais, é feito o agrupamento destes em sequências de três ou de dois. Assim, utilizando, sucessivamente, somadores, para somar os blocos de três produtos parciais, e semi-somadores, para somar os blocos de dois, é feita uma simplificação da operação. Contudo, a conceção do circuito será muito mais complexa, dada a irregularidade deste [13]. Embora substancialmente mais rápido do que o multiplicador de matriz para multiplicadores de bits grandes [14], o multiplicador em árvore de Wallace tem a desvantagem de ser muito irregular, dificultando uma implementação eficaz do circuito. Assim, o algoritmo de Wallace revela-se eficaz para aplicações com números de grandes dimensões, apesar do seu elevado consumo de recursos. Por essa razão, este algoritmo é geralmente evitado em aplicações de baixo consumo, uma vez que, ao utilizar mais recursos, é suscetível a um consumo de energia adicional.

Assim, uma das grandes desvantagens do algoritmo de Wallace é a área do circuito necessária [15]. Desta forma, este algoritmo tem como objetivo agrupar e somar o máximo número possível de produtos parciais, num único passo, sem ter em consideração o número de somadores e semi-somadores utilizados, levando a uma gestão pouco eficiente de recursos. Por outro lado, como referido, a sua vantagem passa por uma redução do tempo de processamento [16].

#### 2.2.6 Gestão do transporte durante a operação

A gestão do transporte durante as somas dos produtos parciais poderá otimizar a execução da operação de multiplicação. Assim, serão apresentados, e relacionados entre si, três

métodos de tratar o transporte durante os cálculos: transporte guardado (Carry Save), transporte antecipado(Carry Lookahead) e propagação de transporte (Carry Propagate).

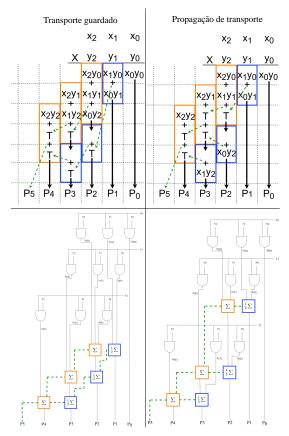

#### 2.2.6.1 Transporte guardado (Carry Save)

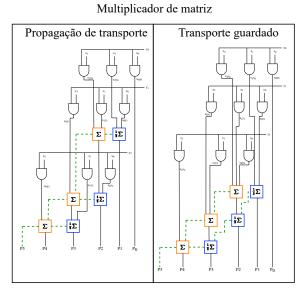

Ao contrário do algoritmo de Wallace, o método baseado no transporte guardado (Carry-Save), também conhecido como multiplicador de Braun [17], não implica uma soma imediatamente após o agrupamento dos produtos parciais. Este algoritmo passa por propagar o transporte paralelamente [18]. Dessa forma, apenas no fim da operação, somará o valor do transporte. O método de transporte guardado, apresentado nas figuras 2.9 e 2.10, poderá possibilitar uma otimização da velocidade de processamento, devido à ligação em paralelo entre somadores. No entanto, para obter estas otimizações irão ser necessárias operações adicionais, com um eventual acrescento de somadores [19] [16] [20].

Figura 2.9: Arquitetura para multiplicação de matriz através do Transporte Guardado, com 3 bits

Figura 2.10: Cálculos para multiplicação com 3 bits, utilizando o Algoritmo com Transporte Guardado

O método do transporte guardado evita gerar o bit de transporte para cada fase na adição, mas guarda-o para a fase seguinte. Desta forma, pretende-se reduzir o tempo de execução relativo à adição dos produtos parciais, ao adiar a propagação do transporte apenas para a última fase das somas parciais [8].

#### 2.2.6.2 Transporte antecipado (Carry Lookahead)

O método do transporte antecipado é uma técnica utilizada para minimizar o tempo de atraso devido à propagação do transporte. A partir de um conjunto de portas lógicas, o transporte antecipado determina o bit de transporte para cada fase de adição. Desta forma, este algoritmo terá uma maior velocidade de processamento do que o método de propagação de transporte [21] e do método de transporte antecipado [22]. No entanto, a implementação do método do transporte antecipado é mais complexa.

#### 2.2.6.3 Propagação de transporte (Carry Propagate)

Enquanto o transporte guardado é projetado para otimizar a velocidade de adição, especialmente quando múltiplas adições precisam de ser realizadas em paralelo, o método de propagação de transporte é uma técnica mais simples e comum em aplicações menos exigentes, em termos de velocidade. Neste método, os transportes são propagados em série, através dos bits somados [23]. Um exemplo de representação deste método, incluído num multiplicador de matriz, está presente nas figuras 2.4 e 2.5, apresentadas anteriormente.

# 2.3 Algoritmos Aproximados

Os métodos anteriormente apresentados são soluções exatas, ou seja, produzem um resultado exato. No entanto, existem também soluções aproximadas e, concedendo uma certa margem de erro no cálculo, o tempo de execução poderá ser reduzido [24].

#### 2.3.1 Tabelas de consulta (Look-Up Tables)

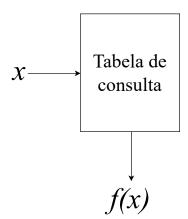

A opção de utilizar tabelas de consulta (Look-Up Tables) envolve uma avaliação com parâmetros como a margem de erro admitida. Com as tabelas de consulta, à medida que a complexidade das operações de multiplicação aumenta, a quantidade de espaço de armazenamento necessário também irá aumentar. Para evitar um uso excessivo de memória, as tabelas de consulta só deverão ser utilizadas com operandos até uma certa dimensão. Dado um x, estas tabelas permitem calcular o resultado diretamente de uma dada função de x, como é apresentado na figura 2.11. A sua exatidão irá variar consoante o número de bits presentes nas tabelas de consulta. Do ponto de vista de execução, poderão existir diferentes abordagens utilizando as tabelas de consulta, nomeadamente se se pretender um sistema sequencial ou baseado em lógica combinatória, incluindo também a hipótese de se utilizar espaços transformados.

Assumindo, como exemplo, um valor constante associado ao multiplicando, a quantidade de resultados possíveis, guardados na coluna de uma tabela de consulta, será de  $2^m$ , com m a representar o número de bits do multiplicador. No entanto, continuará a ser necessária uma grande capacidade de memória. Uma outra forma de reduzir o armazenamento necessário passa por utilizar várias tabelas de consulta para gerar os produtos parciais, durante os cálculos auxiliares. Embora sejam necessárias várias tabelas de consulta, a memória alocada às mesmas será exponencialmente menor [25].

Figura 2.11: Representação de uma tabela de consulta (Look-Up Table)

#### 2.3.2 Espaços Transformados - Logaritmos

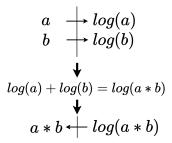

Para utilizar os espaços transformados, através dos logaritmos, terá que se determinar o cálculo dos logaritmos através de uma ou mais tabelas de consulta. A quantidade necessária das mesmas dependerá da conceção do sistema, se consistirá numa lógica sequencial ou combinatória. De notar que, ao utilizar este método, a capacidade de memória necessária poderá tornar-se incomportável.

Se se pretender fazer uma multiplicação utilizando um método baseado, exclusivamente, em lógica combinatória, serão necessárias três tabelas de consulta, uma tabela para a transformada de cada operando, e uma terceira tabela para a transformada inversa. As duas tabelas de consulta irão apresentar o valor do logaritmo, associado ao respetivo operando. Finalmente, com a terceira tabela, será feita a transformada inversa do resultado da soma dos logaritmos, como demonstra a figura 2.12.

Figura 2.12: Representação do espaço transformado, utilizando logaritmos

Num sistema sequencial, a quantidade necessária de tabelas de consulta é menor relativamente a um sistema baseado em lógica combinatória, sendo requerido, no mínimo, apenas uma tabela de consulta. Esta tabela irá ser utilizada para transformar os dois operandos e realizar a transformada inversa. Logo, será necessário realizar um processo iterativo para guardar, temporariamente, os dados, dado que haverá uma única tabela de consulta e várias operações de transformada. Deste modo, cada uma destas ações será efetuada em passos de execução diferentes. Assim, a vantagem deste método é ser possível poupar recursos, ao fazer a multiplicação apenas consultando uma tabela de consulta para os dois operandos, somando o resultado e consultando, uma segunda vez, tabela de consulta para fazer a transformada inversa. No entanto, ao poupar recursos, este método terá de ser sequencial, e não baseado em lógica combinatória.

# Análise de soluções exatas

De modo a proceder a uma análise aprofundada serão examinados os recursos presentes nos vários tipos de multiplicadores de solução exata: multiplicadores de matriz, multiplicadores de Wallace e multiplicadores de Booth. Para as arquiteturas dos multiplicadores, irá ser considerada a otimização da criação dos produtos parciais, da representação de operandos e da estrutura para a redução dos produtos parciais na fase final do processo. No caso do multiplicador de matriz, também será analisado como a gestão do transporte afeta o seu desempenho.

### 3.1 Conceção de cada circuito

A partir dos métodos estudados, projetou-se, numa primeira análise e a um nível prático, uma estratégia de como implementar os algoritmos, concebendo o circuito de cada multiplicador, tendo como objetivo a análise de diferentes hipóteses de implementação da operação de multiplicação em VHDL. Assim, será útil entender a implementação dos algoritmos escolhidos através da aplicação Xilinx ISE. As soluções implementadas são, nomeadamente, multiplicador de Booth, multiplicador de matriz e multiplicador de Wallace. De modo a simular o comportamento de cada algoritmo foram estudadas as respetivas estruturas. Nesta secção será apresentada a conceção de cada arquitetura. Esta consistirá numa estrutura de blocos com as respetivas entradas e saídas dos somadores e semisomadores. A partir dessa estrutura de blocos é feita uma segmentação dos conjuntos de somadores e semi-somadores. Para alguns métodos foi também criado um gerador de código VHDL capaz de automatizar a implementação do código, consoante o número de bits dos operandos. Esta automatização, criada em Python, foi implementada de acordo com as necessidades da análise e as possibilidades de cada método, que dependerão da capacidade de cada algoritmo se manter regular com a variação do número de bits dos operandos. Estes algoritmos estão descritos no Anexo I e podem ser acedidos em https://github. com/TomasGoncalves49917/Gerador-de-multiplicadores-em-codigo-VHDL.git.

#### 3.1.1 Multiplicador de matriz

No multiplicador de matriz, presente na figura 3.1, existirão duas variantes da sua arquitetura envolvendo a gestão do transporte sendo estas a propagação de transporte e transporte guardado.

Figura 3.1: Multiplicador de matriz

#### 3.1.1.1 Método de propagação de transporte

O método de propagação de transporte foca-se em incluir um, ou dois, valores de transporte de uma soma anterior em cada somador, como se constata na figura 2.4, apresentada anteriormente. Desta forma, o transporte "propaga-se" ao longo de todos os somadores.

Figura 3.2: Estrutura de blocos para a multiplicação de matriz através de propagação de transporte

Para compreender a génese do multiplicador de matriz através da propagação de

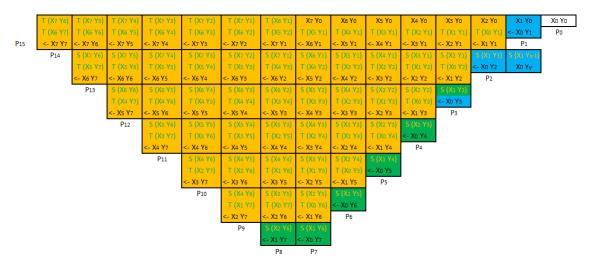

transporte, as colunas da estrutura de blocos, figura 3.2, foram divididas em blocos para determinar a progressão aritmética da soma dos produtos parciais, permitindo construir cada coluna correspondente a cada produto parcial. Esta segmentação está presente na figura 3.3.

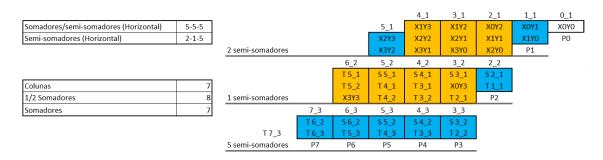

|                                                                                                                                                            | _         |                                                                                                |           |           |                             |          |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------|-----------|-----------|-----------------------------|----------|----------|

| nr coluna=nrbits                                                                                                                                           |           | 2<=nr coluna <nrbits< td=""><td></td><td></td><td></td><td>_</td><td></td></nrbits<>           |           |           |                             | _        |          |

| nrlinha=1                                                                                                                                                  |           | nrlinha=1                                                                                      |           |           | nr coluna=1                 | nı       | coluna=0 |

| T (Xx-1 Yy)                                                                                                                                                | T (X2 Y1) | X(nr coluna) YY (0)                                                                            | X3 Y0     | X2 Y0     | Xx+1 Yy-1                   | X1 Y0    | X0 Y0    |

| T (Xx-2 Yy+1)                                                                                                                                              | T (X1 Y2) | T (Xx-1 Yy)                                                                                    | T (X1 Y1) | T (X0 Y1) | semi-somador: XX(0)         | <- X0 Y1 | P0       |

| XX (decrescente de cima a partir de (nr coluna-1) até 2)                                                                                                   | <- X3 Y1  | XX (decrescente de cima a partir de (nr coluna-1) até 1)                                       | <- X2 Y1  | <- X1 Y1  | semi-somador: YY(nr coluna) |          |          |

| YY (crescente de cima a partir de 1 até (nr coluna -2))                                                                                                    |           | YY (crescente de cima a partir de 1 até (nr coluna -1))                                        |           |           | P1                          | P1       |          |

| 2<=nrlinha <nrcoluna< td=""><td></td><td>2&lt;=nrlinha<nrcoluna< td=""><td></td><td>S (X1 Y1)</td><td></td><td></td><td></td></nrcoluna<></td></nrcoluna<> |           | 2<=nrlinha <nrcoluna< td=""><td></td><td>S (X1 Y1)</td><td></td><td></td><td></td></nrcoluna<> |           | S (X1 Y1) |                             |          |          |

| S (Xx+1 Yy-1)                                                                                                                                              | S (X3 Y1) | S (Xx+1 Yy-1)                                                                                  | S (X2 Y1) | <- X0 Y2  |                             |          |          |

| T (Xx-2 Yy+1)                                                                                                                                              | T (X0 Y3) | T (Xx-1 Yy)                                                                                    | T (X0 Y2) | P2        |                             |          |          |

| XX (decrescente de cima a partir de (nr coluna-1) até 2)                                                                                                   | <- X2 Y2  | XX (decrescente de cima a partir de (nr coluna-1) até 1)                                       | <- X1 Y2  |           |                             |          |          |

| YY (crescente de cima a partir de 1 até (nr coluna -2))                                                                                                    |           | YY (crescente de cima a partir de 1 até (nr coluna -1))                                        |           |           |                             |          |          |

| nrlinha=nrcoluna (semi-somador)                                                                                                                            |           | nrlinha=nrcoluna (semi-somador)                                                                |           |           |                             |          |          |

| S (Xx+1 Yy-1)                                                                                                                                              | S (X2 Y2) | S (Xx+1 Yy-1)                                                                                  | S (X1 Y2) |           |                             |          |          |

| semi-somador: XX(1) YY(nr coluna-1)                                                                                                                        | <- X1 Y3  | semi-somador: XX(0) YY(nr coluna)                                                              | <- X0 Y3  |           |                             |          |          |

| Pnrcoluna                                                                                                                                                  | P4        | Pnrcoluna                                                                                      | P3        | -         |                             |          |          |

Figura 3.3: Segmentação de colunas de somadores e semi-somadores, para a multiplicação de matriz através de propagação de transporte

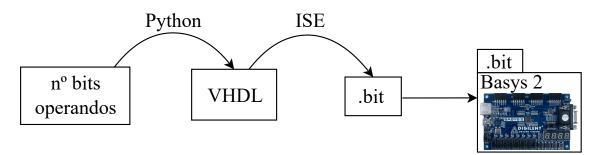

Após feita a segmentação, esta informação foi traduzida para linguagem Python, de forma a gerar automaticamente um ficheiro de texto com o código VHDL que permitirá implementar o multiplicador numa FPGA Basys 2, como é apresentado na figura 3.4. Assim, o processo é dividido em três passos: gerar um ficheiro VHDL através do algoritmo implementado em Python, indicando o número de bits dos operandos; gerar um ficheiro .bit através da aplicação Xilinx ISE; configurar a FPGA com o ficheiro .bit.

Figura 3.4: Processo de geração de código VHDL e a sua implementação numa FPGA

O código em Python é apresentado na figura 3.5 e no anexo I.1. O código, gerado em VHDL, é apresentado na figura 3.6 e no anexo I.2. O código VHDL gerado contém a arquitetura que representa o multiplicador e o código relativo ao *Testbench*, utilizado para a simulação.

Figura 3.5: Extrato do código em Python para gerar código VHDL para a multiplicação de matriz através de propagação de transporte

O código criado, inicia-se através da criação de todos os produtos parciais, e a seguir detalha-se as entradas e saídas de cada somador e semi-somador, tal como é indicado na estrutura de blocos na figura 3.2. O modo de implementação do código permite identificar quantos somadores e semi-somadores são necessários para determinar cada produto parcial, para além de identificar quais os valores de transporte envolvidos. Desta forma, está presente, na figura 3.7, o exemplo de um somador implementado em código VHDL. Na figura 3.6, encontra-se parte do código implementado.

```

begin

and 0(0) \le X(0) and Y(0);

and0(1) <= X(0) and Y(1);

and 1(0) <= X(1) and Y(0);

and 1(1) \le X(1) and Y(1);

--P(0)

P(0) \le and O(0);

--P(1)

coluna1_1: semi_somador port map

(A \Rightarrow and1(0),

B \Rightarrow and0(1),

S \Rightarrow P(1),

Carry_Out => transpO(1));

coluna2_1: somador port map

(A \Rightarrow transp0(1),

B \Rightarrow and1(1),

Carry_In => transp-1(2),

S \Rightarrow somal(1),

Carry Out => transp1(1));

```

Figura 3.6: Extrato do código VHDL, gerado automaticamente, para a multiplicação de matriz através de propagação de transporte, com 2 bits em cada operando

Figura 3.7: Exemplo de um somador implementado em código VHDL, para a multiplicação de matriz através de propagação de transporte

#### 3.1.1.2 Método de transporte guardado

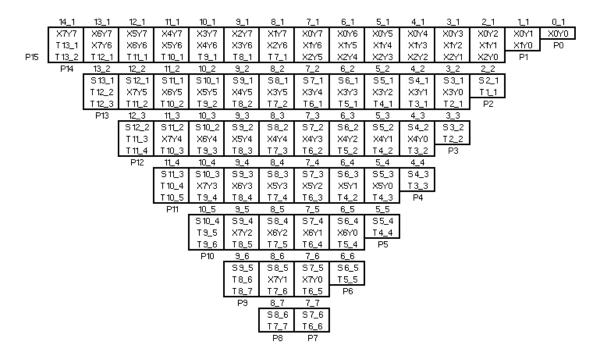

Com o método de transporte guardado, cuja arquitetura se encontra no capítulo anterior, na figura 2.9, as três entradas dos somadores iniciais, responsáveis pelo resultado dos primeiros bits do produto resultante da multiplicação, contêm apenas produtos parciais. Assim, numa primeira fase não haverá uma sequência paralela entre somadores, somando valores de transporte de uma soma anterior, como há no método de propagação de transporte. Deste modo, os valores dos transporte são "guardados" para as somas parciais seguintes, antes de se obter o respetivo bit do produto final. Nas seguintes figuras 3.8, 3.9 estão representadas, respetivamente, a estrutura de blocos e a segmentação feita para a análise comportamental do algoritmo. O código em Python encontra-se representado na figura 3.10 e no anexo I.3. O código em VHDL está presente na figura 3.11 e no anexo I.4.

Figura 3.8: Estrutura de blocos para a multiplicação de matriz através do transporte guardado

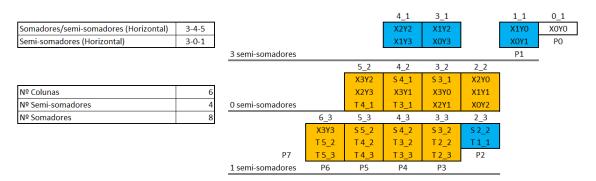

| nr coluna=nrbits                                                                                                                                               |       | 2<=nr coluna <nrbits< td=""><td></td><td></td><td></td><td>_</td><td></td></nrbits<>            |       |       |                            | _    |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------|-------|-------|----------------------------|------|-------------|

| nrlinha=1                                                                                                                                                      | 4_1   | nrlinha=1                                                                                       | 3_1   | 2_1   | nr coluna=1                | 1_1  | nr coluna=0 |

| XX (crescente de cima, X=1)                                                                                                                                    | X1Y3  | XX (crescente de cima, X=0)                                                                     | X0Y3  | X0Y2  | (Xx+1 Yy-1)                | XOY1 | X0Y0        |

| YY (decrescente de cima, Y=(nrcoluna-1))                                                                                                                       | X2Y2  | YY (decrescente de cima, Y=nrcoluna)                                                            | X1Y2  | X1Y1  | semi-somador: XX(0)        | X1Y0 | P0          |

| T (Xnrcoluna-1 Ynrlinha)                                                                                                                                       | T 3_1 |                                                                                                 | X2Y1  | X2Y0  | semi-somador: YY(nr coluna |      |             |

| 2<=nrlinha <nrcoluna< td=""><td>4_2</td><td>2&lt;=nrlinha<nrcoluna< td=""><td>3_2</td><td>2_2</td><td>P1</td><td>P1</td><td></td></nrcoluna<></td></nrcoluna<> | 4_2   | 2<=nrlinha <nrcoluna< td=""><td>3_2</td><td>2_2</td><td>P1</td><td>P1</td><td></td></nrcoluna<> | 3_2   | 2_2   | P1                         | P1   |             |

| S (Xnrcoluna Ynrlinha-1)                                                                                                                                       | S 4_1 | S (Xnrcoluna Ynrlinha-1)                                                                        | S 3_1 | S 2_1 |                            |      |             |

| XX (crescente de cima, X=3)                                                                                                                                    | X3Y1  | XX (crescente de cima, X=3)                                                                     | X3Y0  | T 1_1 |                            |      |             |

| YY (decrescente de cima, Y=(nrcoluna-3))                                                                                                                       |       | YY (decrescente de cima, Y=(nrcoluna-3))                                                        |       | P2    |                            |      |             |

| T (Xnrcoluna-1 Ynrlinha)                                                                                                                                       | T 3_2 | T (Xnrcoluna-1 Ynrlinha-1)                                                                      | T 2_1 |       |                            |      |             |

| nrlinha=nrcoluna (semi-somador)                                                                                                                                | 4_3   | nrlinha=nrcoluna (semi-somador)                                                                 | 3_3   |       |                            |      |             |

| S (Xnrcoluna Ynrlinha-1)                                                                                                                                       | S 4_2 | S (Xnrcoluna Ynrlinha-1)                                                                        | S 3_2 |       |                            |      |             |

| T (Xnrcoluna-1 Ynrlinha-1)                                                                                                                                     | T 3_3 | T (Xnrcoluna-1 Ynrlinha-1)                                                                      | T 2_2 |       |                            |      |             |

| Pnrcoluna                                                                                                                                                      | P4    | Pnrcoluna                                                                                       | Р3    |       |                            |      |             |

Figura 3.9: Segmentação de colunas de somadores e semi-somadores, para a multiplicação de matriz através do transporte guardado

Figura 3.10: Extrato do código em Python para gerar código VHDL para a multiplicação de matriz através do transporte guardado

```

and 0(0) \le X(0) and Y(0);

and\theta(1) \ll X(0) and Y(1);

and1(0) <= X(1) and Y(0);

and1(1) \leq X(1) and Y(1);

--P(0)

P(0) \le and O(0);

--P(1)

coluna1_1: semi_somador port map

(A => and1(0),

B \Rightarrow and O(1),

S \Rightarrow P(1),

Carry Out => transp1 1);

coluna2 1: somador port map

(A => and1(1),

B \Rightarrow and2(0),

Carry In => transp1(1),

S => soma2(1),

Carry_Out => transp2(1));

```

Figura 3.11: Extrato do código VHDL, gerado automaticamente, para a multiplicação de matriz através do transporte guardado, com 2 bits em cada operando

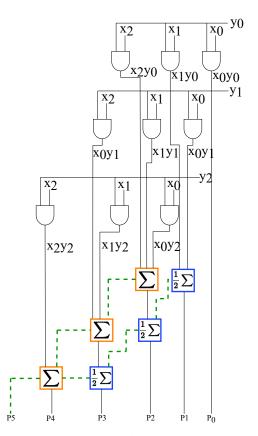

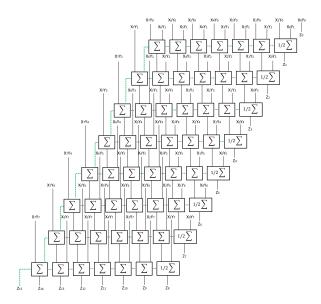

#### 3.1.2 Multiplicador de Wallace

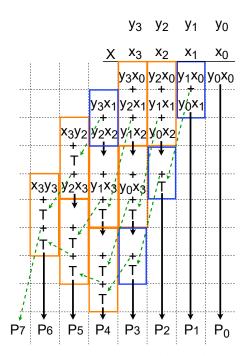

O multiplicador de Wallace é o único algoritmo presente nesta análise cuja topologia não permite que esta seja regular à medida que o número de bits aumenta, devido à sua estrutura não uniforme e à forma como é feito o agrupamento dos produtos parciais para a soma. Ao contrário dos restantes multiplicadores, que contêm a mesma disposição de somadores para cada bit, o multiplicador de Wallace combina e soma os produtos parciais de forma otimizada, o que leva a uma organização não regular. Para análise do algoritmo, foi admitido que cada operando seria composto por 4 bits.

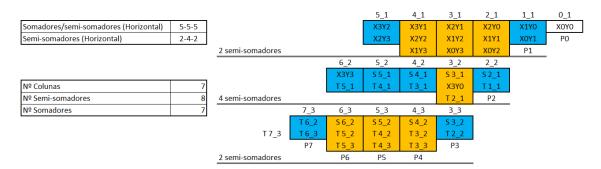

Nesta secção irão ser apresentados quatro métodos, que seguirão a estrutura característica do método de Wallace, que consiste em três fases: criação dos produtos parciais; soma dos produtos parciais e reagrupamento; soma final. Sendo o algoritmo de Wallace irregular, existem diferentes arquiteturas possíveis. Os quatro métodos que serão apresentados foram denominados consoante o número de semi-somadores existente em cada uma das três fases.

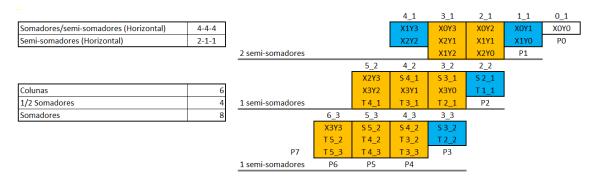

#### 3.1.2.1 Método 2-4-2 com 4 bits

O método 2-4-2 do multiplicador de Wallace, cuja arquitetura foi recolhida por um artigo [26], contém 7 somadores e 8 semi-somadores, conforme indicado na estrutura de blocos, na figura 3.12. A estrutura de blocos é depois traduzida para código VHDL, como se apresenta na figura 3.13 e no anexo I.5.

Figura 3.12: Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-4-2

```

--P(0)

P(0) \le and O(0);

colunal_1: semi_somador port map (A

coluna2_1: somador port map (A => an

coluna2_2: semi_somador port map (A

coluna3_1: somador port map (A => an

coluna3_2: somador port map (A => so

coluna3_3: semi_somador port map (A

coluna4_1: somador port map (A => an

coluna4_2: semi_somador port map (A

coluna4_3: somador port map (A => so

coluna5_1: semi_somador port map (A

coluna5_2: semi_somador port map (A

coluna5 3: somador port map (A => so

coluna6_2: semi_somador port map (A

coluna6_3: somador port map (A => so

coluna7_3: semi_somador port map (A

```

Figura 3.13: Extrato do código VHDL para o multiplicador de Wallace, utilizando o método 2-4-2

#### 3.1.2.2 Método 3-0-1 com 4 bits

O método 3-0-1, baseado na arquitetura de outro artigo [27], contém 8 somadores e 4 semi-somadores, totalizando 12 componentes de adição, um valor inferior relativamente ao método anterior, 2-1-5, que contém 15 componentes. A estrutura de blocos associada é apresentada na figura 3.14 e o código VHDL está presente na figura 3.15 e no anexo I.6.

Figura 3.14: Estrutura de blocos para o multiplicador de Wallace, utilizando o método 3-0-1

```

--P(0)

P(0) <= and0(0);

--P(1)

coluna1_1: semi_somador port map (A => an coluna2_3: semi_somador port map (A => somador port map (A => s

```

Figura 3.15: Extrato do código VHDL para o multiplicador de Wallace, utilizando o método 3-0-1

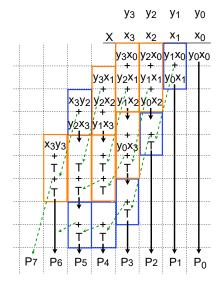

#### 3.1.2.3 Método 2-1-1 e 2-1-5 com 4 bits

Estudando outras estratégias de implementação do multiplicador de Wallace, recorrendo a cálculos de multiplicação, foram implementados dois novos métodos, método 2-1-1 e 2-1-5. Os cálculos para determinar a arquitetura necessária, a estrutura de blocos e o código VHDL relativas ao método 2-1-1, encontram-se nas figuras 3.16, 3.17, 3.18 e no anexo I.7. A mesma informação relativa ao método 2-1-5 encontra-se nas figuras 3.19, 3.20, 3.21 e no anexo I.8.

Figura 3.16: Cálculos para determinar a arquitetura do multiplicador de Wallace utilizando o método 2-1-1

Figura 3.17: Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-1-1

```

--P(0)

P(0) <= and0(0);

--P(1)

coluna1_1: semi_somador port map (A => and6 coluna2_1: semi_somador port map (A => and6 coluna2_2: semi_somador port map (A => and6 coluna3_1: somador port map (A => soma coluna3_2: somador port map (A => soma coluna3_3: semi_somador port map (A => coluna4_1: semi_somador port map (A => coluna4_2: somador port map (A => soma coluna4_3: somador port map (A => soma coluna5_2: somador port map (A => soma coluna5_3: somador port map (A => soma coluna5_3: somador port map (A => soma coluna6_3: somador port map (A => and2 coluna6_3: somador port map (A => and3

```

Figura 3.18: Extrato do código VHDL para o multiplicador de Wallace, utilizando o método 2-1-1

Figura 3.19: Cálculos para determinar a arquitetura do multiplicador de Wallace utilizando o método 2-1-5

Figura 3.20: Estrutura de blocos para o multiplicador de Wallace, utilizando o método 2-1-5

```

--P(0)

P(0) <= and0(0);

--P(1)

coluna1_1: semi_somador port map (A => and(coluna2_2: semi_somador port map (A => and(coluna3_2: somador port map (A => som(coluna3_2: somador port map (A => som(coluna3_3: semi_somador port map (A => som(coluna3_3: semi_somador port map (A => coluna4_1: semi_somador port map (A => coluna4_2: somador port map (A => som(coluna4_3: somador port map (A => som(coluna4_3: somador port map (A => som(coluna5_2: somador port map (A => som(coluna5_3: somador port map (A => som(coluna5_3: somador port map (A => and(coluna6_3: somador po

```

Figura 3.21: Extrato do código VHDL para o multiplicador de Wallace, utilizando o método 2-1-5

#### 3.1.3 Multiplicador de Booth

O multiplicador de Booth, presente na figura 2.6, apresentada anteriormente, baseia-se num método sequencial, com maior velocidade de processamento do que a arquitetura simples de soma e deslocamento [28]. Como referido anteriormente, a sua rapidez devese à possibilidade de verificar dois bits do multiplicador de cada vez, ao passo que a arquitetura de soma e deslocamento verifica bit a bit.

Figura 3.22: Arquitetura de soma e deslocamento e multiplicador de Booth

Através da comparação entre as arquiteturas do algoritmo de soma e deslocamento e do multiplicador de Booth, presente na figura 3.22, verifica-se que são arquiteturas semelhantes. Dessa forma, o multiplicador de Booth é implementado com pequenas alterações

à arquitetura de soma e deslocamento, mas será mais eficiente.

Na figura 3.23 e no anexo I.9, é apresentado o código VHDL que compõe o multiplicador de Booth. Este multiplicador distingue-se dos demais algoritmos, analisados nesta dissertação, como sendo o único método sequencial e tendo a vantagem de permitir operandos com sinal.

```

--cont<-nrbits

for cont in 1 to 4 loop

if (aux(1 downto 0) = "01") then

aux := aux + M pos;

elsif (aux(1 downto 0) = "10") then

aux := aux+M neg;

end if:

--aux[2*nrbits:0] := aux[(2*nrbits+1):1]

--deslocamento aritmético à direita: aux (A|Q|Q-1)

aux(0) := aux(1);

aux(1) := aux(2);

aux(2) := aux(3);

aux(3) := aux(4);

aux(4) := aux(5);

aux(5) := aux(6);

aux(6) := aux(7);

aux(7) := aux(8);

aux(8) := aux(9);

end loop;

--resultado <- A.O

--P[7:0] := aux[8:1]

```

Figura 3.23: Extrato do código VHDL para o multiplicador de Booth

## 3.2 Considerações sobre tempos de propagação

Nas secções 3.2.1 e 3.2.2 descrevem-se duas análises sobre o tempo de processamento dos multiplicadores. São análises não exaustivas, no entanto, considera-se um contributo para outras perspetivas de análise do desempenho dos multiplicadores em trabalhos futuros.

# 3.2.1 Tempo de processamento dos métodos do transporte guardado e da propagação do transporte

Comparando o método de propagação de transporte com o método de transporte guardado, foi possível verificar, pela figura 3.24, que, com o método de propagação de transporte, para o primeiro e segundo somador só será possível realizar a soma sequencialmente, ou seja, após a obtenção do resultado do primeiro e segundo semi-somador, respetivamente. Por outro lado, com o transporte guardado a soma é feita paralelamente. Dessa forma, apenas será necessário aguardar pela conclusão das somas dos semi-somadores na última fase das somas dos produtos parciais. Isto poderá indicar uma redução do tempo

de processamento com o método de transporte guardado, relativamente ao método de propagação de transporte. Tal como este exemplo, poderão existir diferentes estratégias que também poderão influenciar o desempenho do algoritmo.

Figura 3.24: Comparação entre o método com transporte guardado e o método com propagação de transporte

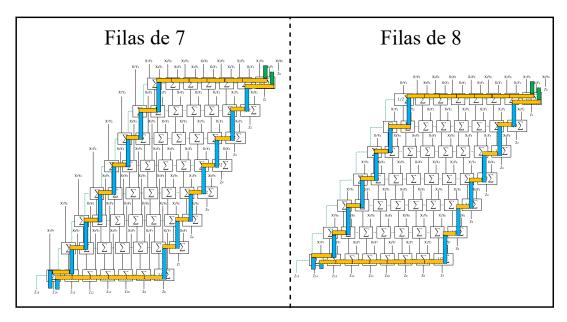

# 3.2.2 Análise de duas variantes de multiplicador de matriz com propagação de transporte

Nas figuras 3.25 e 3.26 estão representadas duas formas diferentes de arquitetura de um multiplicador de matriz com propagação de transporte, sendo que a figura 3.25 contém 7 somadores, ou semi-somadores, em cada fila, e a figura 3.26 contém 8 somadores, ou semi-somadores, em cada fila. Através do caminho crítico, caminho que percorre, com a menor duração, todo o processo de execução, estudar-se-á como, os dois circuitos, com a mesma quantidade de recursos, irão diferir no tempo de execução.

Figura 3.25: Multiplicador de matriz com fila de 7 somadores ou semi-somadores, utilizando propagação de transporte

Figura 3.26: Multiplicador de matriz com fila de 8 somadores ou semi-somadores, utilizando propagação de transporte

A partir dos exemplos de multiplicadores com operandos de 8 bits, presentes nas figuras 3.25 e 3.26, podem-se traçar dois caminhos críticos, expostos na figura 3.27, sendo que cada barra representa um passo de execução. Se se contabilizar os passos de execução, conclui-se que existem 21 passos, utilizando filas de 7 somadores ou semi-somadores. Por outro lado, com filas de 8 somadores ou semi-somadores, existirão 22 passos de execução. Assim, a arquitetura com filas de 7 somadores apresenta-se como a opção com maior velocidade, com os mesmos recursos. Há portanto, possibilidade de, com gestão dos mesmos recursos, otimizar o tempo de processamento. Ao aplicar a mesma análise para