## RAFAEL FILIPE GOMES DE ALMEIDA LOUÇÃO

BsC in Micro and Nanotechnologies Engineering

# BAND PASS NOISE-SHAPING DYNAMIC ELEMENT MATCHING FOR VCM BASED SAR-ASSISTED PIPELINE ADCS

MASTER IN MICRO AND NANOTECHNOLOGIES ENGINEERING NOVA University Lisbon September, 2023

# DEPARTMENT OF MATERIALS SCIENCE

# BAND PASS NOISE-SHAPING DYNAMIC ELEMENT MATCHING FOR VCM BASED SAR-ASSISTED PIPELINE ADCS

## RAFAEL FILIPE GOMES DE ALMEIDA LOUÇÃO

BsC in Micro and Nanotechnologies Engineering

Adviser: Nuno Filipe Silva Veríssimo Paulino

Associate Professor (with Habilitation), NOVA University Lisbon

Co-adviser: João Carlos Palma Goes

Full Professor, NOVA University Lisbon

## Band Pass Noise-Shaping Dynamic Element Matching for VCM based SAR-Assisted Pipeline ADCs

Copyright © Rafael Filipe Gomes de Almeida Loução, NOVA School of Science and Technology, NOVA University Lisbon.

The NOVA School of Science and Technology and the NOVA University Lisbon have the right, perpetual and without geographical boundaries, to file and publish this dissertation through printed copies reproduced on paper or on digital form, or by any other means known or that may be invented, and to disseminate through scientific repositories and admit its copying and distribution for non-commercial, educational or research purposes, as long as credit is given to the author and editor.

To my mom and brothers

## Acknowledgements

Firstly I want to acknowledge that without the partnership between the material science department and the electronic engineering department this project wouldn't have been possible. I am deeply grateful for all the remarkable efforts coming from professors Nuno Paulino, João Goes, Luís Oliveira and João Oliveira that truly helped shape the path I am currently treading. Thank you for all the amazing content procured and given in classes as well as the attentiveness shown whenever hardship rose.

I would like to give a special thank you to my advisers, professor Nuno Paulino and professor João Goes for the guidance given to me throughout the development of this project. I learned a great deal with them, both at academical and personal levels either from the endless email chains or the many zoom meetings, know that I truly appreciate every conversation.

I want to thank the very welcoming team of silicon engineers, from analog to layout to digital, that I interacted with during my internship at AMD, Ireland, especially Lim Peng and Vincent Callaghan who facilitated the integration. Even though the work developed in the internship was separate from that of this dissertation, all the soapboxes, intern meetings and overall gatherings really helped make Ireland a warmer place to write in.

My family above all takes an enormous part in this journey. For every soup that my mother made when I was sick, every late night pick-up after parties, every life lesson and long conversations to all the spoiled "mimo" that we shared, thank you mom I love you, you are and will always be a great part of my heart. I appreciate all the "gooferies" that me and my brothers always had and will continue to have for more years to come. Thank you Ricardo for all the lessons that someday I hope to pass on to my kids. Thank you Rodrigo for coming to my room to do nothing but mess with each other and talk about mindless things. Thank you so much for making home feel like home.

My dearest friends: João, you are one of the most inspirational people I have ever met, thank you for allowing me to learn so much from you every day, the Happiness Enjoyment and fun You bring whenever you are around is out of this world. Ana, thank you for being my partner in crime for all these years and the next to come, you are truly one of a kind. Thank you André for being there allowing me to vent off about most of my difficult moments, giving me advice when I needed it. Thank you Eva for putting up with me every day on end while strolling to Lidl to get lunch.

Thank you all.

"

"Non nobis solum nati sumus. (Not for ourselves alone are we born)"

— **Marcus Tullius Cicero**, De Officiis (Statesman, lawyer, writer, orator, philospher)

### **Abstract**

As the drive for more powerful and capable Analog to Digital Converters (ADCs) increases, so does the need for error mitigation techniques. Components' mismatch significantly degrades the performance of ADCs by introducing non-linearities that cause high energy spurs in its output spectra. Dynamic Element Matching (DEM) techniques allow for the mitigation and filtering of mismatch error's spectral influence, known as noise-shaping. Although these techniques are most commonly used in  $\Sigma\Delta$  ADCs, given that these operate with relatively high Oversampling Ratios (OSRs) and in the low frequency regime, this work will extend a Data Weight Averaging (DWA) DEM technique to the Successive Approximation Register (SAR) architecture enhanced by the pipeline topology for a band-pass operation and a low Oversampling Ratio (OSR). This extension allows for the utilization of filter transfer functions that are embedded in the DEM technique as general as  $H(z) = 1 \pm Z^{-a}$  affecting only the mismatch error. The DEM method, accompanied by an output digital filter, results in the significant increase of the Signal to Noise and Distortion Ratio (SNDR) as well as the Spurious Free Dynamic Range (SFDR) of the converter. This work provides the mathematical demonstration and conceptual explanation, the methods to analyze, and the digital implementation required to realize the referred DEM technique.

Keywords: Mismatch, DEM, DWA, SAR, Noise-Shaping, Band-Pass, OSR, SNDR, SFDR

#### Resumo

À medida que a procura para ADCs mais precisos e capazes aumenta, a necessidade para técnicas de mitigação de erros é maior. A discrepância entre componentes num conversor, (mismatch), deteriora o desempenho significativamente ao introduzir não-linearidades que causam espúrias de alta energia no espetro de saída. Técnicas de DEM permitem a atenuação ou filtragem dos efeitos de mismatch no espetro de saída dos ADCs referida como noise-shaping. Apesar deste tipo de técnicas ser comumente utilizadas em conversores  $\Sigma\Delta$ , porque DEM beneficia das altas taxas de amostragem e operações a baixas frequências destes conversores, o trabalho apresentado estende uma técnica DEM conhecida como DWA a ADCs de topologia SAR assistida por uma estrutura pipeline que possibilitará uma operação de DEM com baixos OSRs e em modos de operação passa-banda. Esta extensão permite a incorporação de filtros gerados pelo algoritmo de DEM de forma geral  $H(z) = 1 \pm Z^{-a}$ . Esta implementação acompanhada por um filtro digital resulta na melhoria apreciável da SNDR bem como da SFDR do conversor. Este trabalho desenvolve a demonstração matemática para a implementação de DEM, realiza uma explicação conceptual para o fenómeno, os tipos de métodos para análise bem como a implementação digital que é capaz de gerar este algoritmo.

Palavras-chave: Mismatch, DEM, DWA, SAR, Noise-Shaping, Passa-Banda, OSR, SNDR, SFDR

## Contents

| Lis | st of F        | igures   |                                                                       | ÌΧ         |  |  |  |

|-----|----------------|----------|-----------------------------------------------------------------------|------------|--|--|--|

| Lis | st of T        | ables    |                                                                       | xii        |  |  |  |

| Ac  | rony           | ms       |                                                                       | xiv        |  |  |  |

| Sy  | mbol           | s        |                                                                       | xv         |  |  |  |

| 1   | 1 Introduction |          |                                                                       |            |  |  |  |

| 2   | SAR            | ADC A    | nalysis                                                               | 3          |  |  |  |

|     | 2.1            | VCM-     | based SAR Stage Functionality                                         | 3          |  |  |  |

|     | 2.2            | Misma    | atch Effects                                                          | 4          |  |  |  |

| 3   | Sam            | pling F  | requency Dependent Dynamic Element Matching Algorithms                | 7          |  |  |  |

|     | 3.1            | Dithe    | ring Effect                                                           | 7          |  |  |  |

|     |                | 3.1.1    | Random Permutation                                                    | 8          |  |  |  |

|     |                | 3.1.2    | Half Random Permutation                                               | 10         |  |  |  |

|     | 3.2            | Seque    | ential Permutations and Noise shaping                                 | 11         |  |  |  |

|     |                | 3.2.1    | MSB Permutation                                                       | 13         |  |  |  |

|     |                | 3.2.2    | Full Resolution Level MSB Permutation                                 | 15         |  |  |  |

| 4   | Sign           | al Depo  | endent Data Weight Averaging                                          | 18         |  |  |  |

|     | 4.1            | Algori   | thm Analysis                                                          | 18         |  |  |  |

|     | 4.2            | Frequ    | ency Domain Contraction                                               | 22         |  |  |  |

|     | 4.3            | Switch   | ning Sequences to obtain other Transfer functions                     | 26         |  |  |  |

| 5   | Fina           | ıl Obser | evations and Conclusions                                              | 30         |  |  |  |

| Bi  | bliog          | raphy    |                                                                       | 31         |  |  |  |

| Αŗ  | pend           | ices     |                                                                       |            |  |  |  |

| A   | VCM            | I-based  | SAR Stage Equations                                                   | <b>3</b> 4 |  |  |  |

| В   | MSI            | B Permu  | utation Equations                                                     | 36         |  |  |  |

| C   | Full           | Resolu   | tion Level MSB Permutation                                            | 37         |  |  |  |

| D   | Algo           | rithms   | Mathematical Description                                              | 39         |  |  |  |

|     | D.1            | Mathe    | ematical Analysis of the Low-Pass Operation DWA                       | 39         |  |  |  |

|     | D.2            | Mathe    | ematical Analysis of the Frequency Contraction Operation of the DWA . | 45         |  |  |  |

| E | Digi | tal Implementation of unified DEM algorithm                                   | 48 |

|---|------|-------------------------------------------------------------------------------|----|

|   |      | DWA                                                                           | 46 |

|   | D.3  | Mathematical Analysis of the general Band-Pass, Odd and Even Operation of the |    |

## **List of Figures**

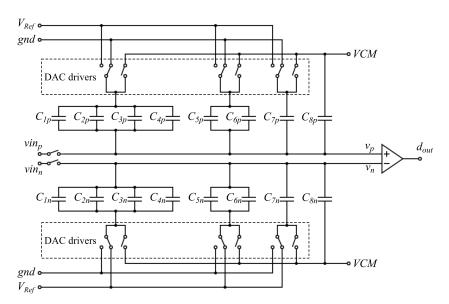

| 2.1  | A  3-bit Common Mode Voltage (VCM) - based  SAR  Analog  to  Digital  Converter  (ADC) / State  Converted  (ADC) / State  (ADC) / State  Converted  (ADC) / State  (ADC) | age |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | with capacitor discrimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3   |

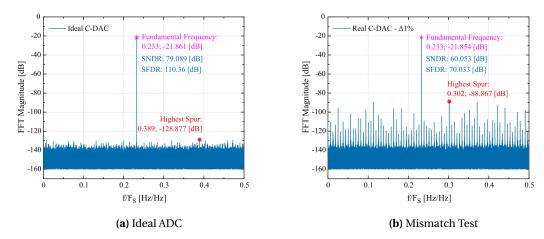

| 2.2  | Output spectra of the pipeline SAR ADC's in a) with ideal capacitors, and in b) with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | mismatch applied to them                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5   |

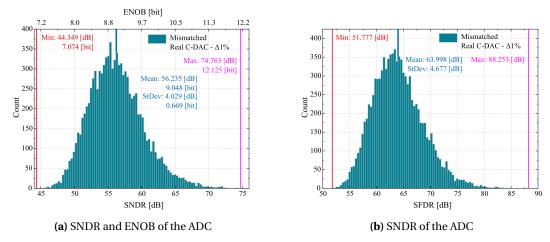

| 2.3  | Monte-Carlo (MC) analysis of the mismatch effect in the output spectra of the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5   |

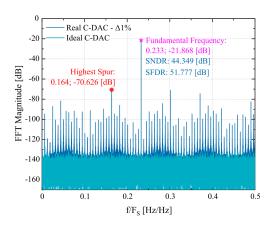

| 2.4  | Comparison of the output spectra of the ADC with mismatch in dark blue, and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | ideal in light blue. This case represents the run out of 10000 MC runs that rendered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | the lowest SNDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6   |

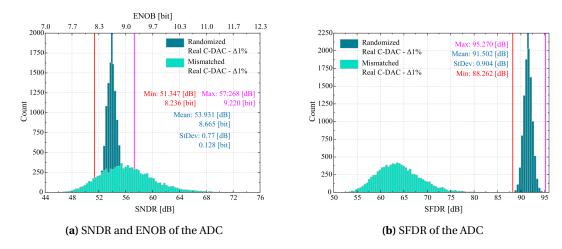

| 3.1  | MC analysis of the randomized and mismatched Capacitive Digital to Analog Con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|      | verter (C-DAC) effect in the output spectra of the ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9   |

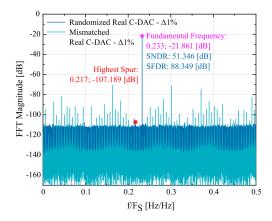

| 3.2  | Comparison of the output spectra of the ADC with randomization in dark blue, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | the mismatch in light blue. This case represents the run out of 10000 MC runs that                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | rendered the lowest SNDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9   |

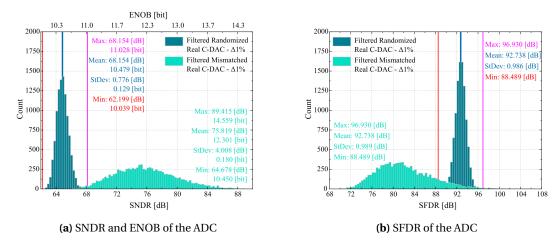

| 3.3  | MC analysis of the randomized and mismatched C-DAC effect in the filtered output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | spectra of the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |

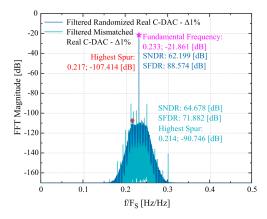

| 3.4  | Comparison of the filtered output spectra of the ADC with randomization in dark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | blue, and the mismatch in light blue. This case represents the run out of 10000 MC $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | runs that rendered the lowest SNDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10  |

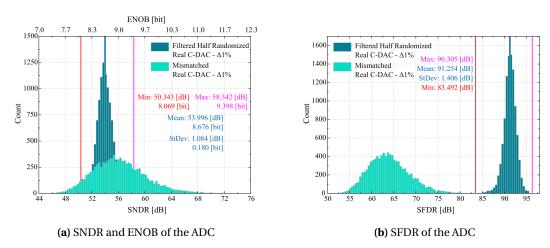

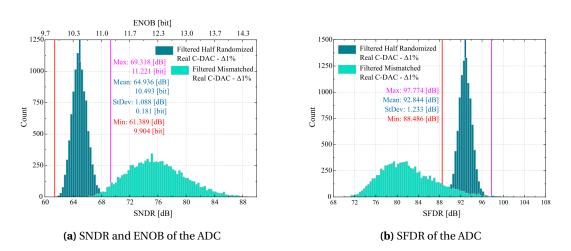

| 3.5  | MC analysis of the half randomized and mismatched C-DAC effect in the output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | spectra of the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11  |

| 3.6  | Comparison of the output spectra of the ADC with the half randomization in dark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | blue, and the mismatch in light blue. This case represents the run out of 10000 MC $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | runs that rendered the lowest SNDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12  |

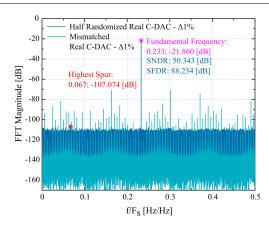

| 3.7  | MC analysis of the half randomized and mismatched C-DAC effect in the filtered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|      | output spectra of the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12  |

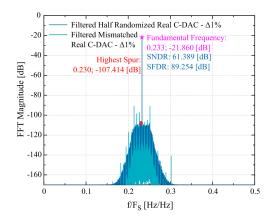

| 3.8  | Comparison of the filtered output spectra of the ADC with the half randomization in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | dark blue, and the mismatch in light blue. This case represents the run out of 10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | MC runs that rendered the lowest SNDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12  |

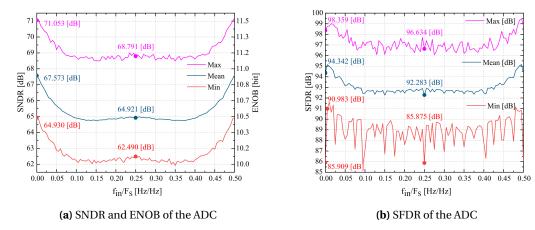

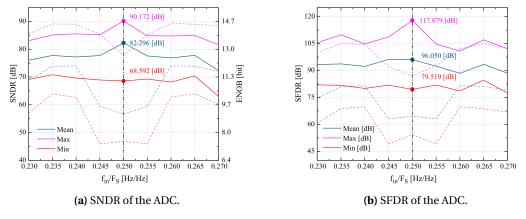

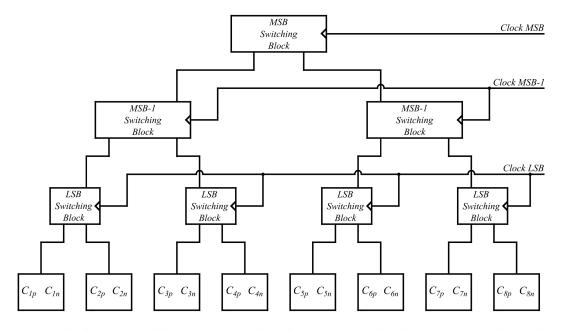

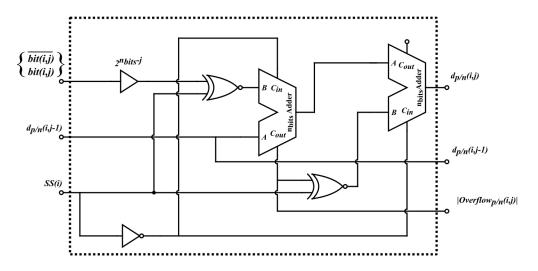

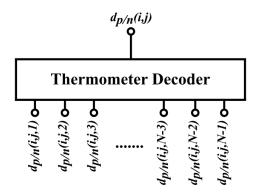

| 3.9  | Performance of an ADC that undergoes Most Significant Bit (MSB) swap, on the first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | stage of resolution 5 bits as the input frequency changes. The data were obtained by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | running 400 MC runs for each frequency swept.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14  |

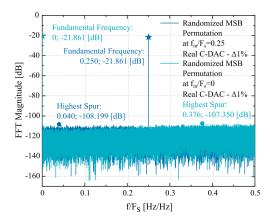

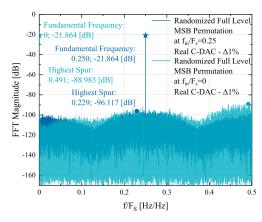

| 3.10 | Output spectra comparison of an ADC that undergoes the randomized MSB per-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | mutation on a 5 bit stage for input frequencies of $f_{in}/F_S = 0$ , in light blue, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | $f_{in}/F_S = 0.25$ , in dark blue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15  |

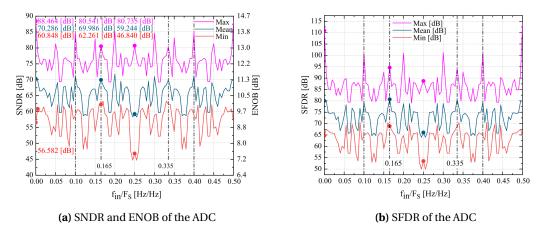

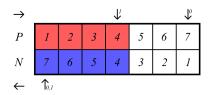

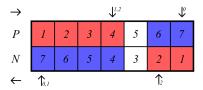

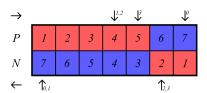

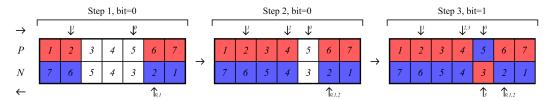

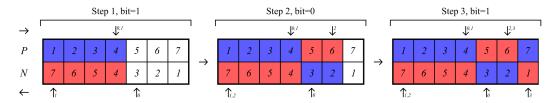

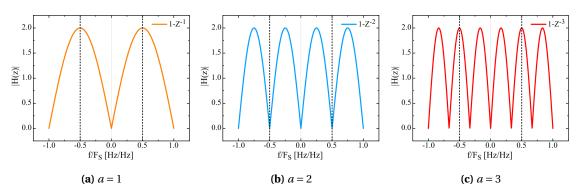

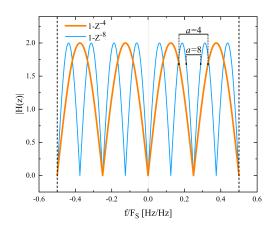

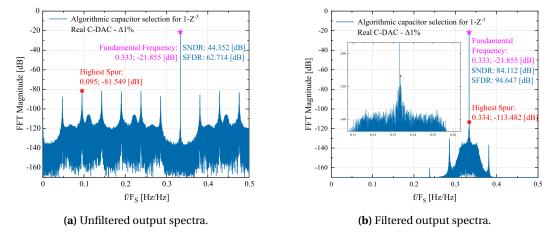

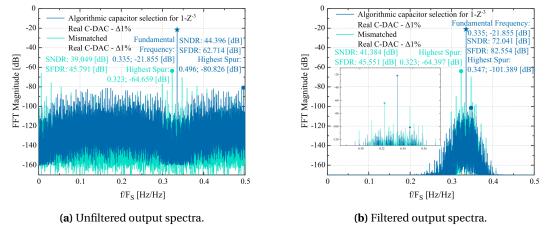

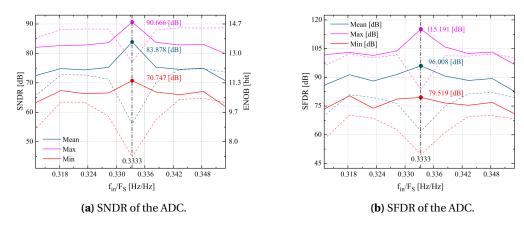

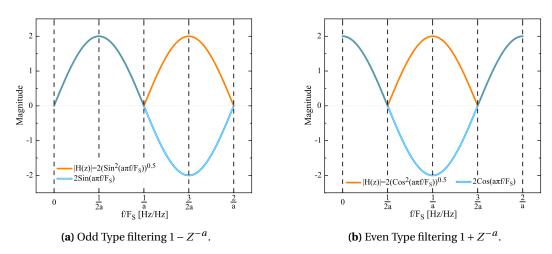

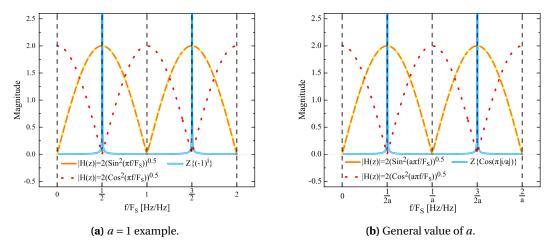

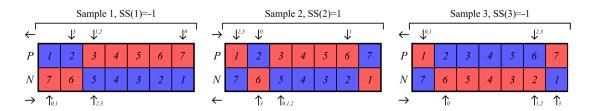

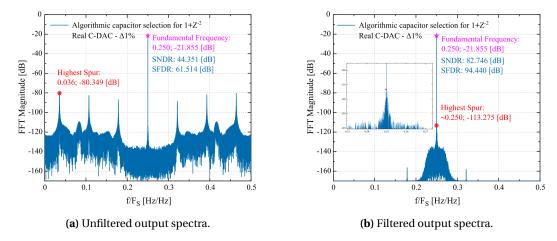

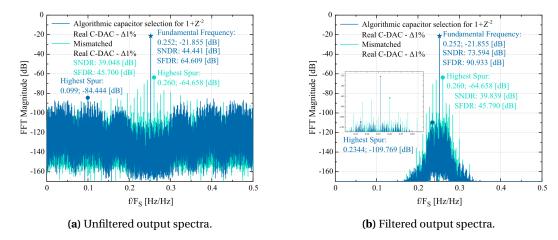

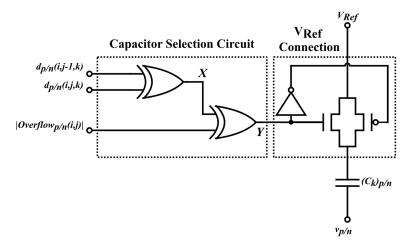

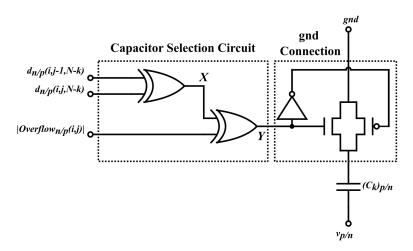

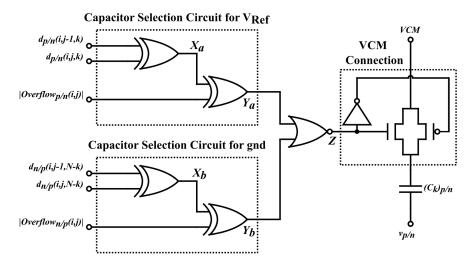

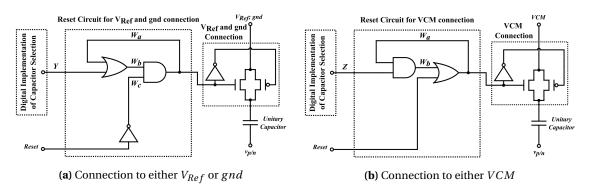

| 3.11 | Performance of an ADC that undergoes non-dithered level 3 MSB swap, on the first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |