# NOVA SCHOOL OF SCIENCE & TECHNOLOGY

### **DEPARTMENT OF MATERIALS SCIENCE**

| Hugo Filipe Matias Viana                                     |  |

|--------------------------------------------------------------|--|

| Bachelor of Sciences in Micro and Nanotechnology Engineering |  |

|                                                              |  |

IMPLEMENTATION OF ACTIVE INDUCTORS WITH OXIDE THIN-FILM TRANSISTORS AND INTEGRATION INTO OSCILLATOR CIRCUITS

MASTER OF SCIENCES IN MICRO AND NANOTECHNOLOGY ENGINEERING NOVA University Lisbon December, 2021

#### **DEPARTAMENT OF MATERIALS SCIENCE**

# IMPLEMENTATION OF ACTIVE INDUCTORS WITH OXIDE THIN-FILM TRANSISTORS AND INTEGRATION INTO OSCILLATOR CIRCUITS

#### **HUGO FILIPE MATIAS VIANA**

Bachelor of Sciences in Micro and Nanotechnology Engineering

Advisor: Prof. Dr. Pedro Miguel Cândido Barquinha, Associate

Professor, NOVA University Lisbon

Co-advisor: Prof. Dr. Pydi Ganga Mamba Bahubalindruni, Assistant

Professor,

Indian Institute of Science Education and Research Bhopal

#### **Examination committee:**

Chairperson: Prof. Dr. Rodrigo Ferrão de Paiva Martins, Full Professor, NOVA

**University Lisbon**

Rapporteur: Prof. Dr. João da Palma Goes, Full Professor, NOVA University

Lisbon

Member: Prof. Dr. Pydi Ganga Mamba Bahubalindruni, Assistant Professor,

Indian Institute of Science and Education and Research Bhopal

MASTER OF SCIENCES IN MICRO AND NANOTECHNOLOGY ENGINEERING

NOVA Univeristy Lisbon December, 2021

| Implementation of Active Inductors with Oxide Thin-Film Transistors and Integration into Oscillator Circuits                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright © Hugo Filipe Matias Viana, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa.                                                                                                                                                                                                                                |

| A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através |

| de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de                                                                                                                                                                                                                                  |

investigação, não comerciais, desde que seja dado crédito ao autor e editor.

Aos meus pais

# **ACKNOWLEDGEMENTS**

Concluding this work is the end of a long and anticipated goal of my life. This results from 5 years of hard work, happiness, tough and good moments, where I would not succeed without the people that walked with me, so I want to appreciate those that were by my side.

A special and a huge thanks to my advisors, professor Ganga and professor Pedro. To professor Ganga, thank you for helping me to understand the concepts and for the availability to clear my doubts. For the innumerous videocalls during these months, even with time zone confusion, even with my English difficulties, you always tried to help me the best you could. To professor Pedro, despite most of the topics being out of your expertise area, you contributed with ideas and ways to overcome and solve the problems that I faced. Thank you also for the understanding on more personal matter when I was going through a less good period, you tried to push me and motivate to achieve good results.

To Uninova and DEEC department for providing the access to machine with Cadence with 130 nm MOS and TFT model that allowed the production of this work.

To all the professors, that one way or another contributed to my success during these academic years. A special thanks to professor Luís Pereira, professor Joana Pinto, professor Rita Branquinho and professor Pedro Barquinha (once again) from DCM since our paths crossed multiples times, and I believe that you always gave your best to teach and motivate us. From DEEC, professor Luís Oliveira, professor Nuno Paulino and professor Maria Helena Fino for taking my electronics knowledge to a higher level.

Obrigado a todos os que fizeram parte do meu percurso académico, que tornaram estes 5 anos muito para além das cadeiras e das horas de estudo, trouxeram momentos e lembranças de companheirismo, interajuda e de amizade:

À minha família de praxe, os meus afilhados Vasco, Pedro e Mariana pela diversão e bons momentos que partilhamos durante os churrascos do meu 2º ano, mesmo agora, depois de 3 anos, continuarmos a ter essa relação. À minha afilhada mais nova, Catarina, obrigado pelo apoio que demonstras e por ajudares a ser melhor pessoa. Aos meus netos, Mané, Bia, Gui, Ricardo, Laura, Matilde, Matita e Diogo por terem contribuído para que a minha experiência de praxe tenha sido melhor.

Ao Freitas, pelas horas de estudo na biblioteca, pelo pior verão da minha vida a estudar quântica, pela camaradagem, pelas aventuras de trotinete a altas horas da noite (com alguns acidentes à mistura), apesar de agora seres emigrante e já não mantermos a mesma proximidade, eu sei que estás a torcer por mim como eu torço por ti. Ao grupo da 202 com várias horas de estudo e outras tantas de procrastinação: à Amanda, pela companhia no estágio, pelos muitos trabalhos feitos juntos, pelas chamadas de atenção merecidas; ao Bernas, pelas horas a jogar *Valorant*, por outras tantas horas postas em trabalho juntos; ao Sabino, pelas conversas sobre tudo e sobre nada com cerveja como companhia; ao Tomás, pelas *heals* no *Valorant*, pelos jantares na cantina; à Joana pelas discussões desde aulas práticas Física I até monografia de MTMP. A todos que participaram neste percurso: Rui, Freire, Leonor, Caril, Diogo, Francisco Silva, Pipo, Maria, Tiago, obrigado.

O meu obrigado aos meus colegas de casa que se tornaram amigos: Filipe aka Jaime pelo apoio, pelos jantares e festas, pela sabedoria e conselhos; Chico pelas horas de jogos desde *CS*, *Valorant*, *League*, etc., pela companhia nas idas ao supermercado, pelas conversas filosóficas ou sem sentido, pela parceria a ver vídeos, músicas, *streams*, por seres a pessoa mais tranquilo que eu alguma vez convivi.

Aos meus amigos da "terrinha": ao André por todos estes anos juntos, nos bons ou maus momentos, pelas saídas, pelas conversas, pelas peladinhas, por tudo e mais alguma coisa, meu irmão. Márcia, Ana Maria, Kika, Teixeira, Zé David, Zé Gusto, Braga, Paulinho, Chico, Cate, Adri e Ventura, obrigado por serem bons e velhos amigos.

A ti, Inês, o meu sincero e mais puro obrigado. Tu, desde o início da nossa história tens sido a minha maior força, o meu porto de abrigo, a minha inspiração e motivadora. Estes últimos tempos teriam muito mais difíceis, se não fosses tu. Contigo, encontrei a cumplicidade, o companheirismo, a felicidade, o amor que eu quero e preciso para o que vem a seguir desta fase. Obrigado pelas refeições fantásticas, pelas séries vistas, pelas noites inesquecíveis do "eixo do mal" aos vídeos de russos e polacos passando pelas músicas lendárias, por seres DJ nas viagens de carro, pelas horas de *Valorant* e *League*, pelas brincadeiras que mantemos. Obrigado por tudo.

À minha família, Tita, Davi e Bruno, que estão sempre disponíveis para me ajudar. A ti, minha mana, obrigado pelo apoio e conselhos, mesmo estando tão distante fisicamente. Ao meu sobrinho mesmo não crescendo contigo, a tua alegria e fofura transpassa a videochamada. Ao resto da família, obrigado.

Para terminar, o meu maior e mais especial agradecimento aos meus pais, Irene e Fernando, a quem dedico também este trabalho, pois sem eles não seria possível chegar onde estou hoje e para onde ambiciono chegar. Sempre estiveram presentes e fizeram de tudo para me dar apoiar e ajudar no que fosse necessário. Sempre educaram o melhor conseguem, sempre me ensinaram a ser uma boa e humilde pessoa, a ter orgulho nas minhas origens e hoje digo: tenho orgulho no homem que sou e donde venho, graças a vocês, por isso, OBRIGADO.

"Engineers must be forever frustrated to continue to design things that work better" (Max Conze – Dyson's ex-CEO)

# **ABSTRACT**

This work aims to investigate the replacement of passive inductors with active inductors (aLs) using amorphous indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFT). The goal of aL is to emulate the inductive behavior associated with passive inductors. The advantage of the former is the small die area, high quality-factor, inductance, and self-resonant frequency tunability.

A simple grounded n-type aL was used to replace the inductor in an inductance-capacitance (LC) oscillator. The LC oscillator is constituted by a cross-couple pair and two aLs. The simple grounded aL configuration was used due to a-IGZO being an n-type semiconductor and also owing to its simplicity, being only built with two transistors and two current sources. These factors allied with the lack of a counterpart p-type amorphous oxide semiconductor make this aL a good fit for the proposed work. The oscillator was simulated using metal-oxide-semiconductor field-effect transistor (MOSFET) and TFTs. The former was simulated with a channel length of 1  $\mu$ m and the latter was simulated with two channel-lengths 10  $\mu$ m and 20  $\mu$ m. The MOS technology simulations were used as a proof-of-concept since these have more accurate models. The oscillation frequency ( $f_{OSC}$ ) and output peak-to-peak voltage swing ( $V_{pp}$ ) were analyzed for both technologies. Temperature sensibility, and phase noise were also examined for the MOS technology.

The MOS oscillators with three different aLs presented an  $f_{\rm OSC}$  between 917 MHz and 2.08 GHz, power consumption from 21 mW to 80 mW, a  $V_{\rm pp}$  of 613 mV up until 1.78 V with a power supply voltage ( $V_{\rm DD}$ ) of 5V. The maximum phase noise was - 92.86 dBc/Hz at an offset of 1 MHz. A 10  $\mu$ m a-IGZO TFTs oscillator produced an  $f_{\rm OSC}$  of 1.21 MHz and a  $V_{\rm pp}$  of 3.83 V, dissipating 533  $\mu$ W for a  $V_{\rm DD}$  of 10V.

**Keywords:** a-IGZO TFT; Active inductor (aL); Simple grounded aL; Cross-couple pair LC-oscillator.

# **RESUMO**

Este trabalho tem como objetivo investigar a substituição de indutores passivos por bobines ativas (aLs), utilizando transístores de filme fino (TFT) de óxido de índio-gálio-zinco amorfo (a-IGZO). O objetivo do aL é emular o comportamento associado aos indutores passivos. As vantagens dos aLs são: pequena área de implementação, alto fator de qualidade e indutância e frequência de ressonância ajustáveis.

Um aL simples conectado à massa foi usado para substituir a bobine no oscilador de indutância-capacitância (oscilador LC). O oscilador LC é constituído por um par cruzado e dois aLs. A utilização da configuração do aL simples conectado à massa deve-se ao facto do a-IGZO ser um semiconductor tipo-n, e à sua simplicidade. Este é apenas constituído por dois transístores tipo-n e duas fontes de corrente. Estes fatores aliados à falta de um óxido semiconductor tipo-p de qualidade torna esta configuração apelativa. A simulação do oscilador foi realizada através das tecnologias de metal-óxido-semicondutor (MOS) e TFT. No caso da primeira, o comprimento de canal ( $L_{\rm CH}$ ) foi de 1  $\mu$ m e no caso da segunda, implementaram-se 2  $L_{\rm CH}$ : 10 e 20  $\mu$ m. As simulações da tecnologia MOS funcionaram com prova de conceito. Analisou-se a frequência de oscilação ( $f_{\rm OSC}$ ) e tensão de pico-a-pico ( $V_{\rm pp}$ ) nos osciladores de ambas as tecnologias. Adicionalmente, a sensibilidade à temperatura e o ruído de fase foram analisados para a tecnologia MOS.

Os osciladores LC implementados com três diferentes aLs utilizando transístores MOS apresentaram  $f_{\rm OSC}$  entre 917 MHz e 2.08 GHz, potência dissipada desde 21 mW até 80 mW e  $V_{\rm pp}$  variando de 613 mV até 1.78 V, utilizando 5 V como fonte de alimentação ( $V_{\rm DD}$ ). O ruído de fase máximo foi de -92.86 dBc/Hz a 1 MHz. O oscilador LC utilizando TFTs produziu uma  $f_{\rm OSC}$  = 1.21 MHz e  $V_{\rm pp}$  = 3.83 V, dissipando 533  $\mu$ W com  $V_{\rm DD}$  = 10 V.

**Palavras-chave:** a-IGZO; Bobine ativa (aL); aL simples conectado à massa; oscilador LC de par cruzado.

# LIST OF CONTENTS

| ACKNOWL     | EDGEMENTS                                    | ix    |

|-------------|----------------------------------------------|-------|

| ABSTRACT    | ·                                            | xiii  |

| RESUMO      |                                              | xv    |

| LIST OF CO  | ONTENTS                                      | xvii  |

| LIST OF FIG | GURES                                        | xix   |

| LIST OF TA  | ABLES                                        | xxi   |

| ACRONYM     | S AND ABBREVIATIONS                          | xxiii |

| SYMBOLS.    |                                              | xxv   |

| 1 MOTIV     | ATION AND OBJECTIVES                         | 1     |

| 2 INTROI    | DUCTION                                      | 3     |

| 2.1 Thi     | n-film transistor                            | 3     |

| 2.1.1       | Working principles of a FET                  | 3     |

| 2.2 Act     | tive inductor                                | 4     |

| 2.2.1       | Working principles of an active inductor     | 4     |

| 2.2.2       | The frequency range of the active inductor   | 5     |

| 2.2.3       | The quality factor of the active inductor    | 6     |

| 2.3 Osc     | cillator                                     | 6     |

| 2.3.1       | Oscillation conditions                       | 6     |

| 3 METHO     | DDOLOGY                                      | 9     |

| 3.1 Cir     | cuit design                                  | 9     |

| 3.2 Cir     | cuit simulation                              | 9     |

| 3.2.1       | MOS technology                               | 9     |

| 3.2.2       | TFT technology                               | 9     |

| 4 RESUL     | TS AND DISCUSSION                            | 11    |

| 4.1 LC      | -oscillator theoretical analysis             | 11    |

| 4.1.1       | Active inductor                              | 11    |

| 4.1.2       | Cross-couple pair                            | 12    |

| 4.1.3       | Oscillations conditions                      | 14    |

| 4.1.4       | Active inductor applied into LC-oscillator   | 14    |

| 4.2 MC      | OS technology design and simulations         | 14    |

| 4.2.1       | aL-based LC-oscillator design and simulation | 14    |

| 4.2.2       | aL RLC equivalent circuit                    | 16    |

| 4.2.3       | Temperature sensibility analysis             | 18    |

|    | 4.2.4                                | Phase noise simulation                       | 21 |

|----|--------------------------------------|----------------------------------------------|----|

|    | 4.3 Oxi                              | de TFT technology simulation and design      | 22 |

|    | 4.3.1                                | aL-based LC-oscillator design and simulation | 22 |

|    | 4.3.2                                | aL RLC equivalent circuit                    | 22 |

| 5  | 5 CONCLUSION AND FUTURE PERSPECTIVES |                                              |    |

| RI | EFERENC                              | ES                                           | 27 |

# LIST OF FIGURES

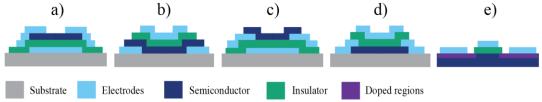

| Figure 1 - Typical structures of FET: a) staggered bottom-gate TFT; b) staggered top-gate TFT; c)                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| coplanar bottom-gate TFT; d) coplanar top-gate TFT; e) MOSFET                                                                                  |

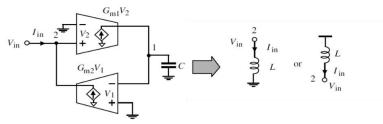

| Figure 2 - Ideal gyrator-C circuit and its equivalent circuit. $V_1$ and $V_2$ are the voltages at nodes 1 and 2,                              |

| respectively. $G_{m_1}$ and $G_{m_2}$ are the transconductance of transconductors 1 and 2, respectively. $C$ is the capacitor                  |

| at node 1. One of the transconductors must have a positive transconductance and the other one must have a                                      |

| negative transconductance (adapted from [8])                                                                                                   |

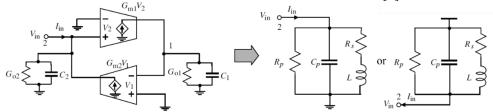

| Figure 3 - Lossy gyrator-C circuit and its equivalent circuit. $V_1$ and $V_2$ are the voltages at nodes 1 and 2,                              |

| respectively. $G_{\rm m_1}$ and $G_{\rm m_2}$ are the transconductance of transconductors 1 and 2, respectively. $G_{\rm o1}$ and $G_{\rm o2}$ |

| represent the total conductances at nodes 1 and 2, respectively. $G_{01}$ includes the finite input impedance of the                           |

| transconductor 2 and the finite output impedance of transconductor 1. $C_1$ and $C_2$ represent the total capacitance                          |

| at nodes 1 and 2, respectively (adapted from [8])                                                                                              |

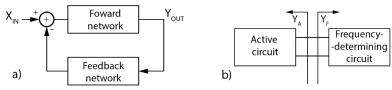

| Figure 4 - Oscillators models: a) feedback model - $X_{IN}$ and $Y_{OUT}$ are the input and output signal; b)                                  |

| negative-resistance model - $Y_A$ is admittance of the active circuit and $Y_F$ is the admittance of frequency-                                |

| determining circuit (adapted from [11])                                                                                                        |

| Figure 5 - a) passive inductor-based LC-oscillator; b) active inductor-based LC-oscillator11                                                   |

| Figure 6 - Simple grounded active inductor: a) schematic; b) high-frequency small-signal equivalent.                                           |

| $M_{aL1}$ is a common-source configuration (forward path) and $M_{aL2}$ is a common-drain configuration (feedback                              |

| path)12                                                                                                                                        |

| Figure 7 - Ideal ross-couple pair: a) schematic; b) small-signal equivalent13                                                                  |

| Figure 8 - Non-ideal cross-couple pair: a) schematic with the parasitic capacitances; b) schematic with                                        |

| parasitic capacitance rearranged using the Miller's theorem; c) small-signal equivalent of b)                                                  |

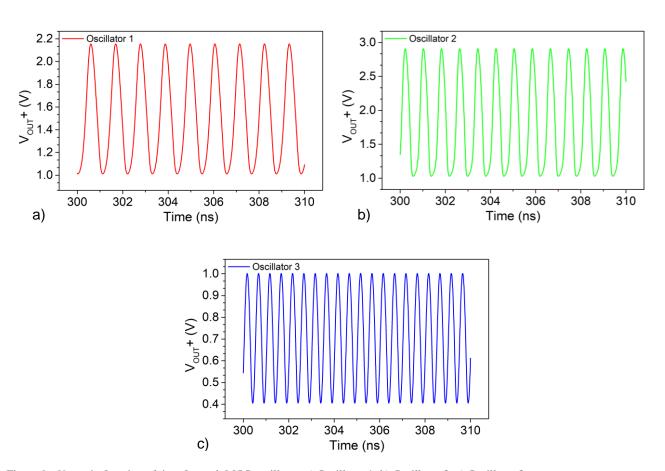

| Figure 9 - V <sub>OUT</sub> + in function of time for each MOS oscillator: a) Oscillator 1; b) Oscillator 2; c) Oscillator                     |

| 3                                                                                                                                              |

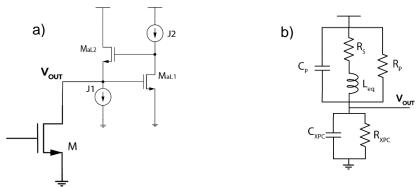

| Figure 10 - One branch of the aL-based LC-oscillator: a) schematic; b) RLC equivalent circuit16                                                |

| Figure 11 - Z-parameters and phase of the RLC equivalent circuit. Real(Z), Imaginary (Z) and phase                                             |

| measurement in function of the frequency: a) Oscillator 1; b) Oscillator 2; c) Oscillator 3                                                    |

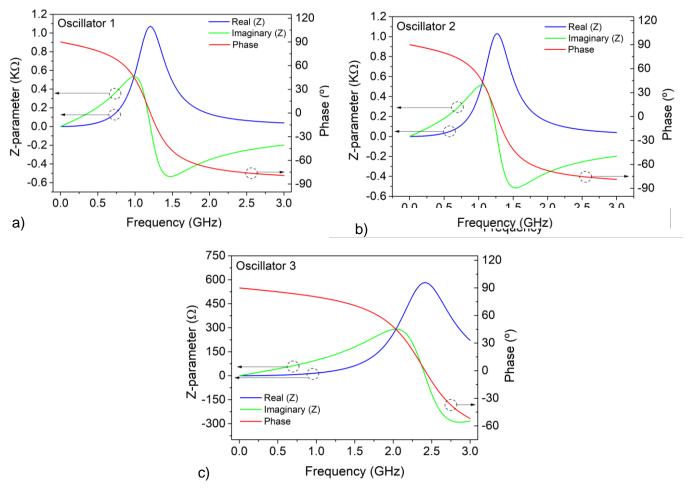

| Figure 12 - Temperature sensibility for each MOS oscillator. a) oscillation frequency; b) power                                                |

| consumption; c) output peak-to-peak voltage                                                                                                    |

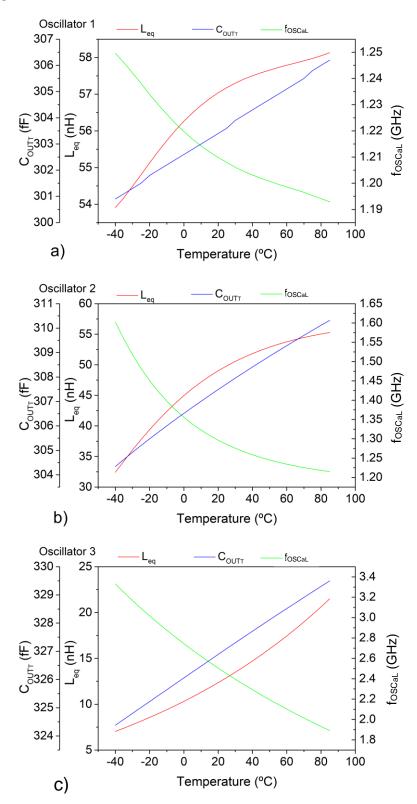

| Figure 13 - $C_{OUT_T}$ , $L_{eq}$ and $f_{OSC_{aL}}$ versus of temperature, being blue, red and green lines, respectively: a)                 |

| Oscillator 1; b) Oscillator 2; c) Oscillator 3.                                                                                                |

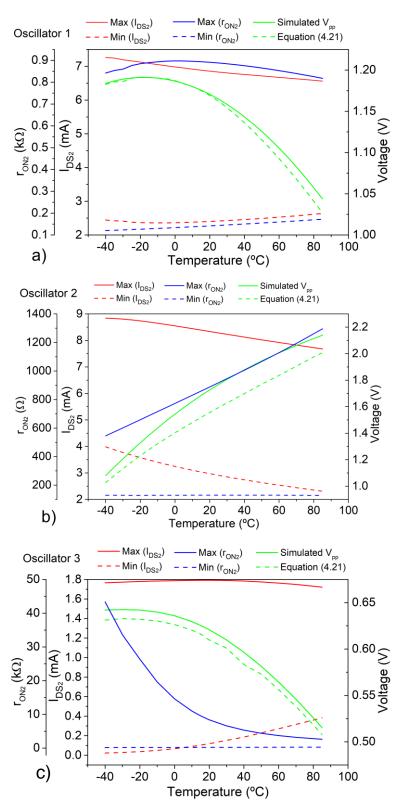

| Figure 14 - Maximum and minimum of $I_{DS_2}$ (red curve) and $r_{ON_2}$ (blue curve) in function of temperature,                              |

| being the maximum the solid line and minimum the dash line. $V_{pp}$ obtained by (4.21) – dash green line – and                                |

| the simulated $V_{pp}$ in function of temperature – solid green line. a) Oscillator 1; b) Oscillator 2; c) Oscillator 3.                       |

| 20                                                                                                                                             |

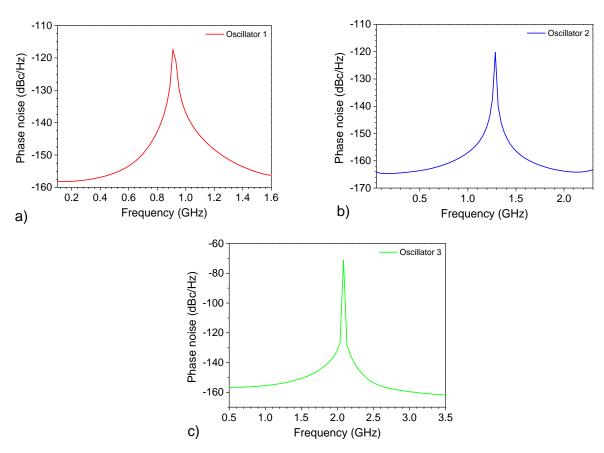

| Figure 15 - Phase noise at 1 MHz offset from the fundamental frequency for each MOS oscillator: a)                                             |

| Oscillator 1; Oscillator 2; c) Oscillator 3.                                                                                                   |

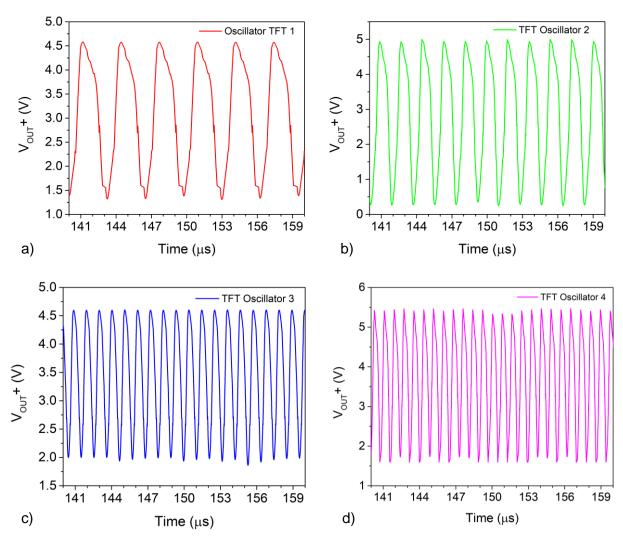

| Figure 16 - $V_{OUT}$ + in function of time for each oxide TFT oscillator: a) Oscillator 1; b) Oscillator 2; c)                                |

| Oscillator 3: d) Oscillator 4                                                                                                                  |

# LIST OF TABLES

| Table 1 - Comparison between the active inductor and passive on-chip inductor (adapted from [8] and                   |

|-----------------------------------------------------------------------------------------------------------------------|

| [9])                                                                                                                  |

| Table 2 - Transistor width (W), number of fingers (NoF) and bias currents (J) for each MOS oscillator.                |

| $V_{\rm DD}$ is 5 V and $L_{\rm CH}$ is 1 $\mu m$ for MOS technology.                                                 |

| Table 3 - Power consumption, $f_{OSCS}$ and $V_{pp}$ for each MOS oscillator.                                         |

| Table 4 - RLC equivalent components values, correspondent to Figure 10 b), respective $f_{\rm OSC_{aL}}$ and relative |

| error for each MOS oscillator                                                                                         |

| Table 5 - Phase noise at 1 MHz of offset for each MOS oscillator, and respective Q-factor at $f_{OSCS}$ 21            |

| Table 6 - Transistor width (W), number of fingers (NoF) and bias currents (J) for each oxide TFT                      |

| oscillator22                                                                                                          |

| Table 7 - Power consumption, $f_{OSCS}$ and $V_{pp}$ for each oxide TFT oscillator                                    |

| Table 8 - RLC equivalent components values, correspondent to Figure 10 b), respective $f_{\rm OSC_{aL}}$ and relative |

| error for each oxide TFT oscillator23                                                                                 |

| Table 9 - State-of-the-art of oscillators using AOS-based oxide TFTs. BG - Bottom gate; RO - ring                     |

| oscillator; SA – Self-aligned; $P_{con}$ – Power consumption. *Estimated from the reports. **Values presented in      |

| μm                                                                                                                    |

# **ACRONYMS AND ABBREVIATIONS**

ADE Analog Design Environment

a-IGZO Amorphous Indium-Gallium-Zinc Oxide

aL Active Inductor

ANN Artificial Neural Network

AOS Amorphous Oxide Semiconductor

CMOS Complementary Metal-Oxide-Semiconductor

D Drain

DC Direct Current

EC Equivalent Circuit

FET Field-Effect Transistor

FoM Figure of Merit

G Gate

hb Harmonic Balance

KCL Kirchhoff's Current Law

LC Inductance-Capacitance

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NoF Number of Finger

Q-factor Quality Factor

RF Radio Frequency

RHP Right-Half Plane

RLC Resistance-Inductance-Capacitance

RO Ring Oscillator

S Source

TFT Thin-Film Transistor

UMC United Microelectronics Corporation

USB Upper Sideband XPC Cross-Couple Pair

# **SYMBOLS**

B Susceptance

$B_A$  Active circuit susceptance

$B_F$  Frequency-determining susceptance

C Capacitance

$C_{\text{DB}}$  Drain-to-bulk capacitance  $C_{\text{GD}}$  Gate-to-drain capacitance  $C_{\text{GS}}$  Gate-to-source capacitance

$C_{\text{OV}}$  Overlap capacitance  $C_{\text{OUT}}$  Output capacitance

$C_{\text{OUT}}$  Total output capacitance

$C_{\text{ox}}$  Specific capacitance of the gate dielectric per unit area

$C_{\rm p}$  Parallel capacitance

$C_{\rm XCP}$  Cross-couple pair parasitic capacitance

fosc Oscillation frequency

$f_{\rm OSC_{aL}}$  Active inductor theoretical oscillation frequency

$f_{OSCS}$  Simulated oscillation frequency  $f_{OSCT}$  Theoretical oscillation frequency

G Conductance

$G_A$  Active circuit conductance  $g_{ds}$  Drain-to-source conductance

$G_F$  Frequency-determining conductance  $G_{\rm m}$  Transconductance of transconductor

g<sub>m</sub> Transconductance of transistor

$G_{\rm o}$  Total conductance

$G_{\rm XCP}$  Cross-couple pair conductance

H(s) Forward transfer function

I Current

$I_{A}$  Active circuit current  $I_{DS}$  Drain-to-Source current

$I_{\mathrm{in}}$  Input current Im Imaginary part  $I_{\mathrm{OUT}}$  Output current j Imaginary number J Current source current

L Inductance  $L_{CH}$  Channel length

$L_{\rm eq}$  Equivalent inductance

Max Maximum

Min Minimum

*R* Resistance

$R_A$  Active circuit resistance

Real part

$R_F$  Frequency-determining resistance  $r_{\text{ON}}$  Drain-to-source ON resistance

$R_{\rm p}$  Parallel resistance  $R_{\rm s}$  Serie resistance

$R_{\rm XCP}$  Cross-couple pair resistance

s Product of imaginary number and angular frequency

t Instant of time

V Voltage

$V_{\rm A}$  Active circuit voltage  $V_{

m DD}$  Power supply voltage  $V_{

m DS}$  Drain-to-Source voltage  $V_{

m GS}$  Gate-to-source voltage

$V_{

m OUT}$  Output voltage

$V_{

m pp}$  Peak-to-peak voltage  $V_{

m TH}$  Threshold voltage W Channel width

X Reactance

$X_A$  Active circuit reactance

$X_F$  Frequency-determining reactance

$X_{\text{OUT}}$  Input signal Y Admittance

Y<sub>A</sub> Active circuit admittance

$Y_{\rm F}$  Frequency-determining admittance

$Y_{\text{OUT}}$  Output signal Z Impedance

Z<sub>A</sub> Active circuit impedance

Z<sub>F</sub> Frequency-determining impedance

$Z_{\text{IN}}$  Input impedance

$\beta(s)$  Feedback transfer function

$\mu$  Mobility

λ Channel length modulation factor

$\omega$  Angular frequency

$\omega_{\text{o}}$  Self-resonant angular frequency  $\omega_{\text{osc}}$  Oscillation angular frequency

$\omega_{\rm p}$  Complex conjugate poles angular frequency

$\omega_{\rm z}$  Zero angular frequency

# 1 MOTIVATION AND OBJECTIVES

In recent years, the demand for low-cost and flexible alternatives to the typical silicon metal-oxide-semiconductor field-effect transistor (MOSFET) technology has been increasing [1]. Amorphous oxide semiconductors (AOS) have been demonstrated as a viable choice, due to their good optical and electrical properties, besides low-temperature depositions, and smooth surfaces [2]. Amorphous indium-gallium-zinc oxide (a-IGZO) is one most studied for this purpose. a-IGZO thin-film transistors (TFTs) are being applied in the design of analog/mixed-signal circuits [3]–[6]. The a-IGZO is an n-type semiconductor, and there is a lack of quality p-type AOS counterpart, which does not allow the use of design technique known as complementary MOS (CMOS) [7].

This work is focused on the application of active inductor (aL) using a-IGZO TFTs. The aLs are characterized for small die area, high quality-factor, inductance and self-resonant frequency tunability [8], [9]. The MOS aL found a multitude of applications, such as bandwidth improvement, oscillators, and filters [8].

The application chosen for this work was the replacement of typical passive inductor of the inductance-capacitance (LC) cross-coupled oscillator to simple grounded aL presented in [10].

Simulations in the Cadence Virtuoso environment were performed using MOS and TFT technologies. MOS technology was applied as a proof-of-concept to design an LC oscillator with different simple grounded aL, verifying the oscillation frequency, output voltage swing, temperature sensibility, and phase noise. Then, an in-house model was used to simulate the a-IGZO TFTs LC oscillator with the simple grounded aLs and attest their performance. There are only a few works exploring aL using TFTs as a substitute for the traditional inductor. These concepts permit the design of kHz-MHz range LC oscillator in small areas and high tunability allowing the design of sensor project or ultimately communication systems [11].

This work received funding from the European Community's H2020 program under grant agreement no. 716510 (ERC-2016-StG TREND).

# 2 INTRODUCTION

In this chapter, the working principles, structures, applications of thin-film transistor (TFT) are introduced in the first topic, as well as the comparison between TFTs and metal-oxide-semiconductor (MOS). Next, available TFT technologies are presented. The increasing demand for circuit design using amorphous oxide semiconductors (AOS) is addressed, with a special focus on amorphous indium-gallium-zinc oxide (a-IGZO) TFTs. Inductive elements are presented in the following topic, highlighting the active inductor (aL), its working and implementation principles, and its frequency range constraints. Lastly, oscillator circuits, respective model and oscillation conditions are described.

#### 2.1 THIN-FILM TRANSISTOR

A TFT is a type of field-effect transistor (FET). Contrarily to MOSFETs, TFTs only have three terminals: gate (G), drain (D), source (S) – there is no bulk terminal due to the substrate being an insulator [2], [3]. The typical structures of TFTs are staggered or coplanar depending if the semiconductor is on the opposite side of the S/D terminals, or the same side, respectively. Besides that, TFTs can be distinguished between the top or bottom gate, depending on if the gate terminal is on top or bottom of the structure [2], [12]. These configurations are presented in Figure 1, as well as the typical structure of MOSFETs. Another major difference among these two types of FET is the channel formation between S and D. The TFT channel is created by an accumulation layer and the MOSFET channel is formed by an inversion region, both at the semiconductor/dielectric interface [2].

Figure 1 - Typical structures of FET: a) staggered bottom-gate TFT; b) staggered top-gate TFT; c) coplanar bottom-gate TFT; d) coplanar top-gate TFT; e) MOSFET.

When compared with MOSFETs, TFTs are more suitable for large-area applications, due to their lower cost [12]. Also, TFTs allow for the integration of devices and circuits on new substrates, which enable new applications, such as flexible displays [12] or paper electronics [2].

There are several different TFTs technologies available: oxide semiconductor, amorphous silicon, low-temperature polycrystalline silicon, and organic semiconductors. In recent years, oxide semiconductor-based TFTs gain more notability, especially AOS. These demonstrate simultaneously good optical and electrical proprieties, besides low-temperature depositions, and smooth surfaces. a-IGZO is the most popular AOS example. Indium-gallium oxide or indium-zinc oxide are other examples [2].

a-IGZO TFTs are already being used in the design of analog/mixed-signal circuits [3]–[6], and these are n-type devices, which means that electrons are responsible for channel accumulation [7]. The major limitation of AOS in circuit design is the lack of a quality p-type counterpart. This makes the well-known complementary MOS (CMOS) design not possible – consistently implemented in MOSFET technology. A solution for this is design techniques like pseudo-CMOS or hybrid-CMOS [7].

#### 2.1.1 Working principles of a FET

TFTs and MOSFETs are ON when the voltage between G and S ( $V_{\rm GS}$ ) is greater than threshold voltage ( $V_{\rm TH}$ ), otherwise, the devices are sub-threshold regime and current that passes through the D and S ( $I_{\rm DS}$ ) is residual (ideally sub-pA). Being ON, the FETs exhibit two regions of operation: linear and saturation region. These are controlled by the voltage applied between the D and S terminals ( $V_{\rm DS}$ ), which affects  $I_{\rm DS}$ . Accordingly, the two operation regimes are described by (2.1), and (2.2), respectively. W is the channel width,  $L_{\rm CH}$  is the channel length,  $\mu$  is the charge carrier mobility,  $C_{\rm OX}$  is the specific capacitance of the G dielectric per

unit area.  $\lambda$  is the channel length modulation factor, which is relevant for short-channel, otherwise, it can be assumed as zero [7].

$$I_{\rm DS} = (W/L_{\rm CH}) \, \mu C_{\rm ox} (V_{\rm GS} - V_{\rm TH}) V_{\rm DS}$$

if  $V_{\rm GS} > V_{\rm TH}$  and  $V_{\rm DS} << V_{\rm GS} - V_{\rm TH}$  (2.1)

$$I_{\rm DS} = (W/2L_{\rm CH}) \,\mu C_{\rm ox} (V_{\rm GS} - V_{\rm TH})^2 (1 + \lambda) V_{\rm DS}$$

if  $V_{\rm GS} > V_{\rm TH}$  and  $V_{\rm DS} > V_{\rm GS} - V_{\rm TH}$  (2.2)

#### 2.2 ACTIVE INDUCTOR

Inductors are employed for different purposes in high-speed analog signal processing: bandwidth improvement, oscillators, impedance matching, radio frequency (RF) bandpass filters, RF phase shifters, amplifiers, and many more applications [8].

Inductor elements are characterized for storing the magnetic field when electrical currents pass through by it [13]. Nowadays, on-chip inductors are widely used when compared with traditional off-chip ones, especially for RF applications. The former presents a smaller size, lower cost, and wider bandwidth characteristics [13]. Therefore, they allow for the integration of inductive elements on a single monolithic substrate [8], [13]. Despite that, on-chip inductors present an moderate quality-factor (Q-factor) when compared with their off-chip counterparts, due to smaller element dimensions and a multilevel fabrication process, which translates to more parasitic capacitances and resistances [13].

The demand for even more compact and tunable inductive elements led to intense research and study on the design of inductors employing active devices [8]. This configuration is known as an aL, and it consists of networks with transistors. aLs under specific direct-current (DC) biasing conditions and signal-swing constraints exhibit inductive behavior in a particular frequency range [8]. Table 1 presents a comparison between aLs and on-chip inductors.

Table 1 - Comparison between the active inductor and passive on-chip inductor (adapted from [8] and [9]).

| Parameter                              | Active inductor  | Passive on-chip inductor |

|----------------------------------------|------------------|--------------------------|

| Area                                   | Small die area   | Large die area           |

| Inductance and self-resonant frequency | Large tunability | Fixed                    |

| Q-factor                               | High and tunable | Low and fixed            |

| Power consumption                      | Significant      | Zero                     |

| Noise performance                      | Poor             | No noise (ideally)       |

| Linearity                              | Poor             | Good                     |

| Electromagnetic Interference           | Insensitive      | Significant              |

#### 2.2.1 Working principles of an active inductor

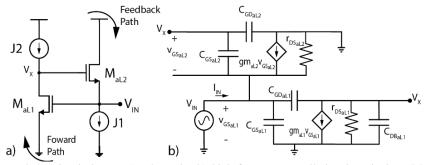

An aL could be built using a gyrator-based synthesis. This is made up of two back-to-back transconductors. If a capacitor is connected to one of the terminals, the network is called a gyrator-C [8].

A lossless single-ended gyrator-C is presented in Figure 2. This means input and output impedances of the transconductors are infinite and the transconductances are constant. Considering (2.3), where Y is the admittance,  $I_{in}$  is the input current,  $V_1$  and  $V_2$  are the voltages at nodes 1 and 2, respectively.  $G_{m_1}$  and  $G_{m_2}$  are the transconductance of transconductors 1 and 2, respectively. s is the product of j (imaginary number) and  $\omega$  (angular frequency). Note that one of the transconductors must have a positive transconductance and the other one must have a negative transconductance [8].

$$Y = \frac{I_{in}}{V_2} = \frac{1}{s\left(\frac{C}{G_{m_1}G_{m_2}}\right)}$$

(2.3)

According to (4), the equivalent inductance of gyrator-C ( $L_{eq}$ ) is given by (4).

Figure 2 - Ideal gyrator-C circuit and its equivalent circuit.  $V_1$  and  $V_2$  are the voltages at nodes 1 and 2, respectively.  $G_{m_1}$  and  $G_{m_2}$  are the transconductance of transconductors 1 and 2, respectively. C is the capacitor at node 1. One of the transconductors must have a positive transconductance and the other one must have a negative transconductance (adapted from [8]).  $L_{\rm eq} = \frac{s\mathcal{C}}{G_{\rm m_1}G_{\rm m_2}}$

$$L_{\rm eq} = \frac{sC}{G_{\rm m_1}G_{\rm m_2}} \tag{2.4}$$

However, in practical applications no transconductor is lossless. Thus, input and output impedance are finite and the transconductance is not constant [8]. The non-ideal gyrator-C aL is shown in Figure 3. To simplify the writing of Kirchhoff's current laws (KCL), it is assumed that the transconductance are constant, as stated in (2.5).  $G_{01}$  and  $G_{02}$  represent the total conductances at nodes 1 and 2, respectively. Notice that  $G_{01}$ includes the finite input impedance of the transconductor 2 and the finite output impedance of transconductor 1.  $C_1$  and  $C_2$  represent the total capacitance at nodes 1 and 2, respectively [8].

$$Y = \frac{I_{in}}{V_2} = sC_2 + G_{o2} + \frac{1}{s\left(\frac{C_1}{G_{m_1}G_{m_2}}\right) + \frac{G_{o1}}{G_{m_1} + G_{m_2}}}$$

(2.5)

Analyzing admittance, which is stated in (2.5), it is possible to infer that the aL resistance-inductancecapacitance (RLC) network equivalent is given by (2.6), being  $L_{eq}$  the inductance,  $C_p$  the parallel capacitance,  $R_p$  the parallel resistance, and  $R_s$  the series resistance. The  $L_{eq}$  value is not affected by the finite impedances.  $R_p$  should be boosted while  $R_s$  should be reduced to minimize the ohmic loss [8].

Figure 3 - Lossy gyrator-C circuit and its equivalent circuit.  $V_1$  and  $V_2$  are the voltages at nodes 1 and 2, respectively.  $G_{m_1}$  and  $G_{m_2}$  are the transconductance of transconductors 1 and 2, respectively.  $G_{01}$  and  $G_{02}$  represent the total conductances at nodes 1 and 2, respectively.  $G_{01}$  includes the finite input impedance of the transconductor 2 and the finite output impedance of transconductor 1.  $C_{11}$ and  $C_2$  represent the total capacitance at nodes 1 and 2, respectively (adapted from [8]).  $L_{\rm eq} = \frac{C_1}{G_{\rm m_1} G_{\rm m_2}}$

$$L_{\rm eq} = \frac{c_1}{G_{\rm m_1} G_{\rm m_2}} \tag{2.6.1}$$

$$C_{\rm p} = C_2 \tag{2.6.2}$$

$$R_{\rm p} = 1/G_{\rm o2} \tag{2.6.3}$$

$$R_{s} = \frac{G_{o1}}{G_{m_{1}}G_{m_{2}}} \tag{2.6.4}$$

#### The frequency range of the active inductor 2.2.2

The lossy aL does not present an inductive behavior across the entire range of frequency, due to the parasitic elements. This results in three behaviors through the frequency spectrum: resistive, inductive, and capacitive [8]. The input impedance  $(Z_{IN})$  of the RLC equivalent circuit (EC) is given by (7).

$$Z_{IN} = \left(\frac{R_{\rm s}}{C_{\rm p}L_{\rm eq}}\right) \frac{s L_{\rm eq}/R_{\rm s} + 1}{s^2 + s\left(\frac{1}{R_{\rm p}C_{\rm p}} + \frac{R_{\rm s}}{L_{\rm eq}}\right) + \frac{R_{\rm p} + R_{\rm s}}{R_{\rm p}C_{\rm p}L_{\rm eq}}}$$

(2.7)

The zero of the impedance  $(\omega_z)$  is related to the lowest frequency that the circuit acts as an inductor and

it is given by (2.8). Lower than that frequency, its behavior is resistive. The self-resonant angular frequency ( $\omega_0$ ) dictates the maximum frequency of the inductive behavior, which is stated by (2.9). At frequencies higher than  $\omega_0$ , the gyrator presents a capacitive characteristic. This results from the meeting of the poles, creating complex conjugate poles ( $\omega_p$ ). Considering  $R_p \gg R_s$ , (2.9) is shortened to (2.10), which is the  $\omega_0$  [8].

$$\omega_{\rm z} = R_{\rm s}/L_{\rm eq} \tag{2.8}$$

$$\omega_{\rm p} = \sqrt{\frac{R_{\rm p} + R_{\rm s}}{R_{\rm p} C_{\rm p} L_{\rm eq}}} \tag{2.9}$$

$$\omega_{\rm p} \approx \sqrt{1/C_{\rm p}L_{\rm eq}} = \omega_{\rm o}$$

(2.10)

#### 2.2.3 The quality factor of the active inductor

There are different definitions of the Q-factor of an inductor. The most general is defined as the ratio of magnetic energy stored to its ohmic loss in one oscillation cycle, as described by (2.11). Also, (2.11) can be interpreted as the ratio between the inductive reactance and the resistance, as presented in (2.12) [8]. The terms are the imaginary ( $Im[Z_{IN}]$ ) and real part ( $Re[Z_{IN}]$ ) of  $Z_{IN}$ . Combining (2.12) and (2.7), results in (2.13) [8].

$$Q-factor_1 = 2\pi \frac{\text{Net magnetic energy stored}}{\text{Energy dissipated in one cycle}}$$

(2.11)

$$Q-factor_2 = Im[Z_{IN}]/Re[Z_{IN}]$$

(2.12)

$$Q-factor_3 = \left(\frac{\omega L_{eq}}{R_s}\right) \frac{R_p}{R_p + R_s + (\omega L_{eq})^2 / R_s} \left(1 - \frac{R_p^2 C_p}{L} - \omega^2 L_{eq} C_p\right)$$

(2.13)

#### 2.3 OSCILLATOR

An oscillator is a circuit that generates a periodic signal without any input signal [14]. They are applied in communication systems and instrumentation [11].

There are several oscillator topologies, and these can be based on different principles of implementation. Oscillators can be categorized into two major classes: relaxation oscillators and harmonic oscillators. Harmonic oscillators deliver a near-sinusoidal signal with good phase noise and high spectral purity. Relaxation oscillators are usually characterized by a poor phase noise and high harmonic content, as the circuit switches intermittently between two astable equilibrium states [11].

The LC oscillator and ring oscillator are two examples of harmonic oscillators. The first is a lumped resonator-based oscillator. To design this oscillator, an inductor and a capacitor are necessary (two forms of reactive components), to achieve complex poles. The ring-oscillator is a non-resonator-based oscillator example that only requires either capacitors or inductors (one type of reactive element). However, the presence of resistive elements and feedback is vital for non-resonator-based oscillator implementation [15].

#### 2.3.1 Oscillation conditions

There are two models to analyze an oscillator: feedback model and negative resistance model [11], [15]. The model utilized depends on the oscillators' configuration and characteristics [11].

Oscillators analyzed by the feedback model can be separated into a forward network and feedback network [11], as shown in Figure 4 a). The negative resistance model can be decomposed into a one-port active circuit and a one-port frequency-determining circuit, as presented in Figure 4 b). The active circuit goal is to create a small-signal negative resistance on the operating point of the oscillator, and it is characterized by the admittance  $Y_A$  (or impedance  $Z_A$ ). The frequency-determining circuit is typically a linear time-invariant circuit, and it is signal independent, being characterized by the admittance  $Y_F$  (or impedance  $Z_F$ ). When connected, the characteristics of both blocks will determine the oscillation frequency [11].

#### 2.3.1.1 Steady-state oscillation conditions

The feedback model's transfer function  $Y_{OUT}/X_{OUT}$  is given by (2.14), where H(s) is the forward transfer

function and  $\beta(s)$  is the feedback transfer function, as presented in Figure 4 a) [15].

Figure 4 - Oscillators models: a) feedback model -  $Y_{\text{IN}}$  and  $Y_{\text{OUT}}$  are the input and output signal; b) negative-resistance model -  $Y_{\text{A}}$  is admittance of the active circuit and  $Y_{\text{F}}$  is the admittance of frequency-determining circuit (adapted from [11]).

$$\frac{Y_{\text{out}}}{X_{\text{in}}} = \frac{H(s)}{1 + H(s)\beta(s)} \tag{2.14}$$

In the steady-state, an oscillator must fulfill the conditions of the Barkhausen's criteria to oscillate. The first condition is known as the "gain condition" and the second one is named as "phase condition". The Barkhausen's criteria conditions are stated in (2.15.1) and (2.15.2), respectively [15], [16].

$$|H(s)\beta(s)| = 1$$

(2.15.1)

$$\angle H(s)\beta(s) = 180^{\circ} \tag{2.15.2}$$

The negative resistance model, as aforementioned is described by  $Y_A$  (or  $Z_A^{-1}$ ) and  $Y_F$  (or  $Z_F^{-1}$ ) –Figure 4 b). These admittances can be separated in their conductance (*G*) and susceptance (*B*) at a determined angular frequency ( $\omega$ ), as presented in (2.16) and (2.17), respectively [15], [16].

$$Y_{A}(\omega) = G_{A}(\omega) + jB_{A}(\omega)$$

(2.16)

$$Y_{\rm F}(\omega) = G_{\rm F}(\omega) + jB_{\rm F}(\omega) \tag{2.17}$$

To oscillate in the steady-state, an oscillator analyzed by the negative resistance model must satisfy the conditions stated in (19), where  $\omega_{osc}$  is the oscillation angular frequency [15], [16].

$$G_{\rm A}(\omega_{\rm osc}) + G_{\rm F}(\omega_{\rm osc}) = 0 \tag{2.18.1}$$

$$B_{\rm A}(\omega_{\rm osc}) + B_{\rm F}(\omega_{\rm osc}) = 0 \tag{2.18.2}$$

#### 2.3.1.1 Start-up conditions

The steady-state does not predict the start-up conditions of an oscillator. The oscillator must start to oscillate in an autonomously way when the circuit is switched on, usually triggered by the noise of the system [15].

To ensure that oscillation begins, the open loop gain of the feedback model should be greater than one, as stated in (2.19). The phase condition is described by (2.15.2) [15]. To convert the start-up conditions to the steady-state conditions, there are two mechanisms to reduce the open-loop gain to the conditions presented in (2.15), being automatic gain control and self-limiting [15].

$$|H(s)\beta(s)| > 1 \tag{2.19}$$

The conductance start-up conditions of the negative resistance model are described by (2.20) and the susptance condition continues to follow (2.18.2). Active circuit conductance should be negative enough to cancel the losses of the frequency-determining circuit to start the oscillation [15], [16].

$$G_{\mathcal{A}}(\omega_{\text{osc}}) + G_{\mathcal{F}}(\omega_{\text{osc}}) < 0 \tag{2.20}$$

#### 2.3.1.1 Complex conjugate poles

As discussed, an oscillator must fulfill the start-up conditions. Despite these being necessary, they are not sufficient for the circuit to start to oscillate. The circuitry must have a pair of complex-conjugate poles in the right-half plane (RHP) [11], [15], [16]. These poles are responsible for the input signal growth. Ultimately, this increase is restricted by nonlinearities in the circuit [11], [16].

<sup>1 –</sup> Or impedances for a series circuit:  $Z_A(\omega) = R_A(\omega) + jX_A(\omega)$  and  $Z_F(\omega) = R_F(\omega) + jX_F(\omega)$ , R is resistance and X is reactance. The subscript A and F denote active circuit and frequency-determining circuit, respectively. (2.19.2) condition become  $X_A(\omega_{osc}) + X_F(\omega_{osc}) = 0$ . (2.18.1) condition becomes  $R_A(\omega_{osc}) + R_F(\omega_{osc}) = 0$  and (2.20) condition becomes  $R_A(\omega_{osc}) + R_F(\omega_{osc}) < 0$  [11], [15].

# 3 METHODOLOGY

In this section, simulation methodology is described. All the designs and the simulations were carried out using the Cadence® Virtuoso® Analog Design Environment (ADE). This section is divided into two subsections: MOS and TFT technology.

In the first subsection, MOS technology is used as a proof-of-concept, applying the United Microelectronics Corporation (UMC) 130 nm library. The design requirements for the oscillator and aL are then explained. Next, simulations are described. The second subsection is related to TFT technology design and simulations, where an in-house model is used.

#### 3.1 CIRCUIT DESIGN

The oscillator and aL schematics were inserted into Virtuoso® ADE. Here, voltages, currents, and transistors dimensions were defined. As aforementioned, due to a-IGZO being an n-type semiconductor and AOS not having a quality p-type counterpart, only n-type transistors were used during the design.

The oscillator was designed using the negative resistance model. According to (2.20), the sum of  $G_A$  and  $G_F$  must be lower than zero. In the steady-state condition, the sum of  $G_A$  and  $G_F$  must be equal to zero, as stated in (2.18.1). (2.18.2) dictates that  $B_A$  and  $B_F$  must be symmetric. Hence, the transistor dimensions and bias conditions were selected to fulfill the oscillations conditions, using the MOS and TFT technologies.

#### 3.2 CIRCUIT SIMULATION

#### 3.2.1 MOS technology

The UMC 130 nm library was employed for MOS simulation in the MOS technology. Due to MOS technology having a more developed and precise model, it was applied as a proof-of-concept.

#### 3.2.1.1 Oscillator simulation

A DC analysis was run to check if all the transistors were in the pretended operating regime – for this work, all the transistors must be in the saturation region. A transient analysis was performed. The stop time was defined to be sufficiently large to observe multiple oscillations. The circuit takes a few periods to achieve the steady-state, so the oscillation frequency ( $f_{OSC}$ ) and peak-to-peak voltage ( $V_{pp}$ ) of the output voltage ( $V_{OUT}$ ) are extracted accordingly.

A temperature sweep from -40  $^{\circ}$ C to +85  $^{\circ}$ C (industrial temperature range [17]) was performed to infer the oscillator temperature sensibility.

To find the oscillator phase noise it was necessary to perform two analyses: a harmonic balance (hb) and an hb noise analysis. To execute the former, stop time and fundamental oscillation were the same used and obtained from the transient analysis. The latter analysis' goal was to measure the upper sideband (USB) contribution.

#### 3.2.1.2 aL simulation

The aL RLC EC parameters were obtained using the DC operating point. The half of the circuit was considered to perform the simulation. A scattering-parameters (S-parameters) analysis was performed, namely the impedance parameters (Z-parameters). From this analysis, it is possible to observe the  $Im[Z_{IN}]$ ,  $Re[Z_{IN}]$ , and phase of RLC equivalent circuit.

#### 3.2.2 TFT technology

The model used in Cadence® Virtuoso® for TFT simulation was an in-house model, reported in [3]. The model consists of a TFT EC, which involves the parasitic elements ( $C_{GS}$  and  $C_{GD}$ ) between the different electrodes and a dependent current source represents the current between the S and D electrodes. An individual artificial neural network (ANN) was developed for each element. Then, the device model was achieved by linking the ANNs as per the EC. The resulting model was implemented in Verilog-A for circuit simulations,

allowing to predict with good accuracy the device's static and dynamic behavior [3]. The oscillator and aL design followed the same methodology presented in section 3.1. However, the transistor model was the Verilog-A in-house model.

#### 3.2.2.1 Oscillator and aL simulation

The oscillator and aL simulation were carried out using the Virtuoso® ADE. Analogous to the procedure described in Oscillator simulation and aL simulation, A DC analysis was performed to ensure that the transistors were in the saturation region, being followed by a transient simulation. The  $V_{\rm pp}$  and  $f_{\rm OSC}$  measurements were extracted once the oscillations were stabilized.

Due to the used TFTs model [3], it is not possible to infer about the oscillator temperature sensibility. In the same way, it is not possible to perform the oscillator phase noise.

# 4 RESULTS AND DISCUSSION

Firstly, the LC-oscillator theoretical is analyzed in this section, including aL and XPC circuit analyses. Next, MOS technology implementation and results are discussed, focusing on the design and simulations. Then, TFT design and simulations of the aL-based LC-oscillator are examined.

### 4.1 LC-OSCILLATOR THEORETICAL ANALYSIS

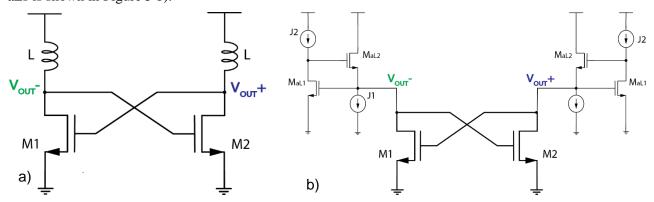

The LC-oscillator consists of an LC tank and a negative resistance. Usually, this circuit is made with a passive inductor and a cross-couple pair (XCP) – Figure 5 a). These are extensively employed in wireless communications, with multiple works reported. The main advantage of the passive inductor is the low level of phase noise [8]. The theoretical  $f_{OSC}$  of the LC-oscillator ( $f_{OSC_T}$ ) is presented in (4.1), where L is the inductance and  $C_{OUT}$  is the capacitance associated with the output node.

$$f_{\rm OSC_T} = \frac{1}{2\pi\sqrt{LC_{\rm OUT}}}\tag{4.1}$$

The goal of this work is to replace the passive inductor with an aL, due to the advantages mentioned in Table 1. The oscillator was analyzed according to the negative resistance model. So, as previously mentioned in section 2.3.1, the oscillator is divided into an active circuit and frequency-determining circuit. The former was achieved using an XCP and the latter one applying aLs. The schematic of the oscillator implemented with aLs is shown in Figure 5 b).

Figure 5 - a) passive inductor-based LC-oscillator; b) active inductor-based LC-oscillator.

The LC-oscillator presents a basic working principle. Output voltage ( $V_{\rm OUT}$ ) can be extracted at the drain of M<sub>1</sub> or M<sub>2</sub>, being labeled  $V_{\rm OUT}$ — and  $V_{\rm OUT}$ +, respectively. At oscillation frequency (which corresponds to the self-resonant frequency) the impedance of the circuit is resistive since the inductance and capacitance cancel each other [18]. Therefore,  $V_{\rm OUT}$  can be approximated by (4.2), where  $I_{\rm OUT_{1,2}}$  is the  $I_{\rm DS}$  that passes through transistor M<sub>1,2</sub>,  $r_{\rm ON_{1,2}}$  is the D to S ON-resistance of M<sub>1,2</sub> and t is an instant of time [18].  $V_{\rm OUT}$ + is high and  $V_{\rm OUT}$ — is low when the transistor M<sub>1</sub> is in the saturation regime and M<sub>2</sub> is in the linear regime, which corresponds to  $I_{\rm OUT_2}$  being low and  $r_{\rm ON_2}$  being in its maximum. Oppositely,  $V_{\rm OUT}$ + is low and  $V_{\rm OUT}$ — is high when the transistor M<sub>1</sub> and M<sub>2</sub> are in triode and saturation regions, respectively. These conditions match  $I_{\rm OUT_2}$  being high and  $r_{\rm ON_2}$  low.

$$V_{\text{OUT}^{-,+}}(t) = I_{\text{OUT}_{1,2}}(t) \cdot r_{\text{ON}_{1,2}}(t)$$

(4.2)

# 4.1.1 Active inductor

As described in section 2.2.1, an aL requires a transconductor with negative transconductance and the other must produce positive transconductance. One of the simplest aL configurations is a common-source as negative transconductor and a common-drain as positive transconductor [8], [19]. This configuration was introduced by M. Ismail et al. in [10] and it is shown in Figure 6, being only constituted by n-type transistors. Additionally, the current sources currents  $J_1$  and  $J_2$  are responsible for polarizing the circuit, ensuring that all

the transistors work in the saturation regime [8], [19]. The intrinsic parasitic capacitances are exploited, instead of the typical grounded capacitor of the gyrator-C architecture [10], [20].

The input impedance ( $Z_{IN}$ ) of the circuit is given by (4.3), after the cancelation of non-dominant terms [8]. C is the capacitance,  $g_{ds}$  is the D to S conductance,  $g_{m}$  is the transconductance. The subscripts GS and GD refer to the quantity between the G and S, G and D, respectively. The subscripts aL1 and aL2 are associated with aL transistors  $M_{aL1}$  and  $M_{aL2}$ , respectively.

Figure 6 - Simple grounded active inductor: a) schematic; b) high-frequency small-signal equivalent.  $M_{aL1}$  is a common-source configuration (forward path) and  $M_{aL2}$  is a common-drain configuration (feedback path).

$$Z_{\rm IN} = \frac{C_{\rm GS_{aL2}} s + g_{\rm ds_{aL1}}}{C_{\rm GS_{aL1}} C_{\rm GS_{aL2}} s^2 + (C_{\rm GS_{aL2}} g_{\rm m_{aL1}} + C_{\rm GS_{aL1}} g_{\rm ds_{aL1}}) s + g_{\rm m_{aL1}} g_{\rm m_{aL2}} + g_{\rm ds_{aL1}} g_{\rm m_{aL1}}}$$

(4.3)

From (4.3), it is possible to extract the RLC EC, as stated (2.7), resulting in (4.4.1).

$$L_{\rm eq} = \frac{C_{\rm GS_{aL2}}}{g_{\rm m_{aL1}}g_{\rm m_{aL2}}} \tag{4.4.1}$$

$$R_{\rm S} = \frac{g_{\rm ds_{aL1}}}{g_{\rm m_{aL1}}g_{\rm m_{aL2}}} \tag{4.4.2}$$

$$C_{\rm p} = C_{\rm GS_{aL1}} \tag{4.4.3}$$

$$R_{\rm p} = \frac{1}{g_{\rm m_{al.1}}} \tag{4.4.4}$$

The aL frequency range is also dictated by  $Z_{IN}$ , namely the self-resonant frequency and the zero, which are given by (4.5) and (4.6), respectively.

$$\omega_{\rm o} = \sqrt{\frac{g_{\rm m_{aL1}}g_{\rm m_{aL2}}}{C_{\rm GS_{aL1}}C_{\rm GS_{aL2}}}} \tag{4.5}$$

$$\omega_{\rm z} = \frac{g_{\rm ds_{aL1}}}{C_{\rm GS_{aL2}}} \tag{4.6}$$

Considering  $R_p$  and  $R_s$  in (4.4), it is possible to conclude that  $R_p$  is much greater than  $R_s$ , so the Q-factor in (2.13) becomes (4.7).

$$Q_3 \approx \frac{R_{\rm p}}{\omega L_{\rm eq}} = \frac{g_{\rm m_{al.2}}}{\omega C_{\rm GS_{al.2}}} \tag{4.7}$$

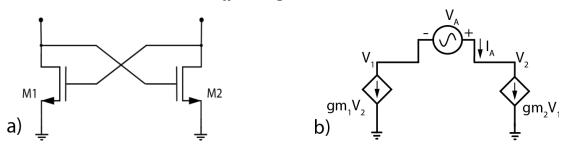

# 4.1.2 Cross-couple pair

The XCP role is to compensate losses of the frequency-determining circuit, through the generation of negative conductance/resistance (-G /-R) [16]. Without XCP, the oscillation decays exponentially, therefore XCP allows oscillation sustainability [16]. M<sub>1</sub> gate is connected to M<sub>2</sub> drain and vice-versa, thus the naming "cross-couple pair". In this section, the XCP is analyzed.

Initially, the XCP impedance is analyzed considering an ideal transistor, being the small-signal only represented as a simple voltage-dependent current source, without considering  $g_{ds}$  and the parasitic capacitors [16]. This representation is shown in Figure 7.

$I_A$  is described in (4.8). The subscript 1 and 2 are related to transistors 1 and 2, respectively. The XCP is a symmetric circuit, which means that the dimensions of the transistors and bias conditions are equal. This implies that the  $g_m$ s are equal, and consequently, from (4.8) is possible to infer (4.9).  $V_A$  is given by (4.10), and combining it with (4.9),  $V_A$  is shortened to (4.11).

$$I_{A} = g_{m_1} V_2 = -g_{m_2} V_1 \tag{4.8}$$

$$V_1 = -V_2 (4.9)$$

$$V_{\rm A} = V_1 - V_2 \tag{4.10}$$

$$V_{\rm A} = 2V_2 = -2V_1 \tag{4.11}$$

The output admittance of the ideal XCP,  $Y_A$ , is given by (4.12).

$$Y_{A} = \frac{I_{A}}{V_{A}} = \frac{g_{\rm m}V_{1}}{-2V_{1}} = -\frac{g_{\rm m}}{2} \tag{4.12}$$

Figure 7 - Ideal ross-couple pair: a) schematic; b) small-signal equivalent.

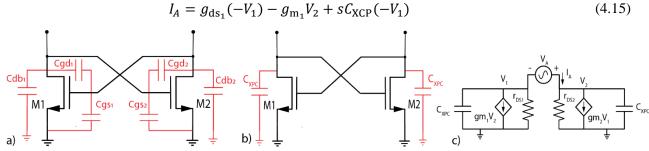

Now considering the capacitances and  $g_{ds}$ , XCP is presented in Figure 8 a). The capacitors  $C_{GD1}$  and  $C_{GD2}$  are in parallel, connected between  $V_1$  and  $V_2$ . However, the capacitors  $C_{GD1}$  and  $C_{GD2}$  are not in parallel with  $C_{GS1}$  and  $C_{DB2}$ . Nevertheless,  $C_{GD1}$  and  $C_{GD2}$  can be rearranged to be connected to the ground, using Miller's theorem, resulting in total XCP parasitic capacitance ( $C_{XCP}$ ) [16]. With this reorganization, all the capacitors are in parallel, resulting in (4.13), as shown in Figure 8 b). (4.13) is shortened to (4.14), due to the symmetry of the circuit.

$$C_{XCP} = 2(C_{GD_1} + C_{GD_2}) + C_{GS_1} + C_{DB_2}$$

(4.13)

$$C_{\text{XCP}} = 4 C_{\text{GD}_{1,2}} + C_{\text{GS}_{1,2}} + C_{\text{DB}_{1,2}}$$

(4.14)

The KCL is applied to the XCP EC presented in Figure 8 c),  $I_A$  is given by (4.15). The subscripts 1 and 2 correspond to transistors  $M_1$  and  $M_2$ , respectively.

Figure 8 - Non-ideal cross-couple pair: a) schematic with the parasitic capacitances; b) schematic with parasitic capacitance rearranged using the Miller's theorem; c) small-signal equivalent of b).

$V_{\rm A}$  is given by (4.11), so combining it with (4.15), the non-ideal XCP admittance is presented in (4.16).

$$Y_{A} = -\frac{g_{\rm m} - g_{\rm ds}}{2} + \frac{sC_{\rm XCP}}{2} \tag{4.16}$$

# 4.1.3 Oscillations conditions

For the circuit to oscillate, it must fulfill the oscillation conditions previously described in section 2.3.1. So, it is possible to apply these conditions to the LC-oscillator with aLs. Therefore, to start oscillation, the negative conductance of XCP ( $G_{XCP}$ ) must cancel the aL conductance ( $G_F$ ). This condition is given by (4.17) [16].

$$-\frac{g_{\rm m} - g_{\rm ds}}{2} + \frac{G_{\rm F}}{2} < 0 \Rightarrow \frac{(g_{\rm m} - g_{\rm ds})}{G_{\rm F}} > 1 \tag{4.17}$$

# 4.1.4 Active inductor applied into LC-oscillator

The aL is integrated with the XCP to produce oscillation, as aforementioned. When integrated, the aL changes its impedance across the frequency due to the impedance associated with XCP. Consequently, the oscillation frequency of the LC-oscillator is lowered, because of the parasitic capacitance of the XCP at the output node. The most relevant parameter affected is  $C_p$ , where the total output capacitance ( $C_{OUT_T}$ ) is given by (4.18). Therefore, (4.1) becomes (4.19) – theoretical  $f_{OSC}$  of aL-based LC-oscillator ( $f_{OSC_{aL}}$ ).

$$C_{\text{OUT}_{\text{T}}} = C_{\text{p}} + C_{\text{XCP}} \tag{4.18}$$

$$f_{\rm OSC_{aL}} = \frac{1}{2\pi\sqrt{C_{\rm OUT_T}L_{\rm eq}}} \tag{4.19}$$

# 4.2 MOS TECHNOLOGY DESIGN AND SIMULATIONS

# 4.2.1 aL-based LC-oscillator design and simulation

The LC-oscillator was designed following section 3.1. The XCP and three aLs with different transistors dimensions, number of fingers (NoF), and bias conditions were implemented. Variables are presented in Table 2. In these cases, oscillation conditions were verified. During this work, the MOS  $L_{\rm CH}$  is 1  $\mu$ m and the power supply voltage ( $V_{\rm DD}$ ) is 5 V. It is important to notice that the simulated transistors feature a thick gate dielectric, otherwise, the devices would reach breakdown for this  $V_{\rm DD}$ . The choice of this  $L_{\rm CH}$  was to achieve results more comparable to oxide TFT technology.

Table 2 - Transistor width (W), number of fingers (NoF) and bias currents (J) for each MOS oscillator.  $V_{DD}$  is 5 V and  $L_{CH}$  is 1  $\mu$ m for MOS technology.

| OSCILLATOR                                       | 1       | 2       | 3       |

|--------------------------------------------------|---------|---------|---------|

| W <sub>1,2</sub> [NoF] (μm)                      | 25 [20] | 25 [20] | 25 [20] |

| $W_{\mathrm{aL1}}[\mathrm{NoF}]~(\mu\mathrm{m})$ | 5 [1]   | 5 [1]   | 10 [1]  |

| $W_{\rm aL2}$ [NoF] ( $\mu$ m)                   | 12 [1]  | 24 [1]  | 12 [1]  |

| $J_{1}\left( \mu \mathrm{A}\right)$              | 100     | 100     | 500     |

| $J_2$ (mA)                                       | 1.5     | 1.5     | 0.5     |

The MOS oscillator was simulated with the different aLs, according to the procedure described in section 3.2.1.1. A DC analysis ensured that all transistors were in the saturation region. A transient analysis was performed, and the results are presented in Figure 9. The power consumption, simulated  $f_{\rm OSC}$  ( $f_{\rm OSCS}$ ), and  $V_{\rm pp}$  are shown in Table 3, where  $V_{\rm pp}$  is given by (4.20), being  $Max(V_{\rm OUT})$  and  $Min(V_{\rm OUT})$  the maximum and minimum of  $V_{\rm OUT}$ , respectively. All these simulations were carried out at 27 °C – room temperature.

$$V_{\rm pp} = Max(V_{\rm OUT}) - Min(V_{\rm OUT}) \tag{4.20}$$

The bias conditions directly affect the power consumption. The power consumption of oscillators was reduced when the bias currents also decreased, as it is possible to observe in Table 3 when comparing oscillators 1 and 2 with oscillator 3. Besides that, greater  $W/L_{CH}$  produces more  $I_{DS}$  in the saturation regime (same voltage conditions), which translates to higher power dissipation. Oscillators 1 and 2 are examples of this, since the transistor  $M_{aL2}$  of the first oscillator has twice the W of the second, resulting in power consumption increase.

The  $L_{\rm eq}$  is given by (2.6.1), so an increase in the  $W/L_{\rm CH}$  ratio of transistor  $M_{\rm al.2}$  generates a decrease in the inductance value, since the  $g_{\rm mal.2}$  value increases more than the  $C_{\rm GSal.2}$  value. Therefore, the  $f_{\rm OSC}$  will increase. To prove this, the  $C_{\rm GS}/g_{\rm m}$  ratio was derived and is given by (4.21), where  $C_{\rm OV}$  is the overlap capacitance [7], [21]. The  $M_{\rm al.2}$ 's  $L_{\rm CH}$  and  $C_{\rm OX}$  are the same and  $V_{\rm TH}$  is approximately equal in both situations. When  $M_{\rm al.2}$ 's W is wider, the  $V_{\rm DS}$  to ensure saturation is lower, because, being the drain voltage equal to  $V_{\rm DD}$ , the source voltage is lower, consequently,  $V_{\rm GS}$  is higher (gate voltage remains constant with the same bias conditions and same dimensions  $M_{\rm al.1}$ ), resulting in a smaller  $C_{\rm GS}/g_{\rm m}$  and, consequently, in a lower  $L_{\rm eq}$ . The results can be observed comparing oscillators 1 and 2, where the  $W/L_{\rm CH}$  of  $M_{\rm al.2}$  of former was twice the one of the latter.

In the same way, increasing the  $W/L_{CH}$  ratio of  $M_{aL1}$  resulted in a lower  $L_{eq}$ , due to increase of  $g_{mall}$ . Additionally, larger W will drop  $V_{DS}$  of transistor  $M_{aL1}$ , but, as source is connected to ground, so the drain will decrease. As drain voltage the  $M_{aL1}$ and  $M_{aL2}$ gate  $V_{\rm GS}$  of  $M_{\rm aL2}$  also decreases, therefore, the  $C_{\rm GS}/g_{\rm m}$   $M_{\rm aL2}$  ratio declines, and  $L_{\rm eq}$  is reduced. On the other hand, larger  $W/L_{CH}$  ratio of  $M_{aL1}$  also increases  $C_{GSaL1}$ , which impacts  $C_p$  and consequently,  $C_{OUT_T}$ . As increase of  $g_m$ is more significant than  $C_{GS}$ ,  $f_{OSC}$  increases. An example of this effect are oscillators 1 and 3, since the W of the former is half of the latter and, nevertheless, foscs of the oscillator 3 is more than the double.

$Figure \ 9 - V_{OUT} + in \ function \ of \ time \ for \ each \ MOS \ oscillator: a) \ Oscillator \ 1; b) \ Oscillator \ 2; c) \ Oscillator \ 3.$

$$\frac{C_{\rm GS}}{g_{\rm m}} = \frac{\frac{2}{3}WL_{\rm CH}C_{\rm OX} + WC_{\rm OV}}{\frac{W}{L_{\rm CH}}C_{\rm OX}(V_{\rm GS} - V_{\rm TH})} \approx \frac{2L_{\rm CH}^2C_{\rm OX}}{3(V_{\rm GS} - V_{\rm TH})}$$

(4.21)

At the output node,  $I_{DSaL2}$  is divided into  $J_1$  and  $I_{DS1,2}$ . Since  $J_1$  is an ideal and constant current source, so the  $I_{DSaL2} - J_1$  results in  $I_{DS1,2}$ , which is the  $I_{OUT1,2}$ . Thus, a greater  $W/L_{CH}$  ratio of  $M_{aL2}$  increases  $I_{DS2}$ , keeping the same  $J_1$  value, and consequently, increases  $V_{pp}$ . On other hand, increasing  $J_1$  produces a signal with a small  $V_{pp}$ , as it is possible to verify in oscillator 3 when compared with oscillator 1. It is noteworthy, that changing dimensions and/or bias conditions affect all characteristics at the same time, so a careful trade-off must be considered to optimize the aL to a given application.

| Table 3 - Power | consumption, foscs | and $V_{pp}$ for $\epsilon$ | each MOS oscillator. |

|-----------------|--------------------|-----------------------------|----------------------|

|-----------------|--------------------|-----------------------------|----------------------|

| OSCILLATOR                          | 1       | 2       | 3       |

|-------------------------------------|---------|---------|---------|

| Power consumption (mW)              | 65.0    | 80.1    | 21.2    |

| $f_{ m OSC_S}\left( { m Hz}  ight)$ | 917.2 M | 1.279 G | 2.080 G |

| $V_{ m pp}$ (V)                     | 1.16    | 1.78    | 0.613   |

# 4.2.2 aL RLC equivalent circuit

To infer on the origins of the different oscillation patterns shown above, the aLs were substituted by their RLC EC (Figure 10). Only one branch of the circuit was considered. The parameters are calculated using (4.4) through LC-oscillator DC operations points, following the procedure of section 3.2.1.2. The  $f_{\rm OSCaL}$  stated in (4.19) is used to confirm the  $f_{\rm OSCs}$ . The component values are present in Table 4, as well as the  $f_{\rm OSCaL}$  and the respective relative error.

Figure 10 - One branch of the aL-based LC-oscillator: a) schematic; b) RLC equivalent circuit.

An S-parameters analysis was performed on the circuit present in Figure 10 b), namely regarding Z-parameters. The goal of this simulation was to observe the output impedance of the circuit across the frequency range and confirm the  $f_{\rm OSCS}$  obtained in Table 3 and presented in Figure 11. The error is resulting from the approximation made in (4.4), just dominant terms were considered, so RLC components values present a difference to those that aL generates.

Table 4 confirms the expected conclusion about feature size and/or bias conditions were correct. Since  $L_{eq}$  decreases with higher  $W/L_{CH}$  ratio of  $M_{aL2}$ , visible in oscillator 1 and 2. The inductance also decreases with higher  $W/L_{CH}$  ratio of  $M_{aL1}$ , as it is possible to observe in oscillator 3. Analogously,  $C_p$  is also affected by the ratio of  $M_{aL1}$  since it raises the parasitic capacitance.

To measure the oscillators' temperature sensibility, a temperature sweep from -40 °C until 85 °C was performed as previously described. Figure 12 shows the power consumption,  $f_{OSC}$ , and  $V_{pp}$  variations across the temperature sweep for all oscillators. The oscillators presented lower  $f_{OSC}$  when the temperature was higher.

$f_{\rm OSC_{aL}}$  depends on equivalent inductance and total parasitic capacitance, as presented in (4.19):  $C_{\rm OUT_T}$  presented an almost linear dependency across temperature range as presented in Figure 13. Simultaneously,  $L_{\rm eq}$  also increased with temperature. Therefore, as  $f_{\rm OSC}$  is inversely proportional to the square root of the product between the output capacitances and inductance, it is possible to conclude that  $f_{\rm OSC_{aL}}$  is inversely proportional

Figure 11 - Z-parameters and phase of the RLC equivalent circuit. Real(Z), Imaginary (Z) and phase measurement in function of the frequency: a) Oscillator 1; b) Oscillator 2; c) Oscillator 3.

### to the temperature, as presented in Figure 13, in agreement with $f_{OSCS}$ .

Table 4 - RLC equivalent components values, correspondent to Figure 10 b), respective  $f_{OSCaL}$  and relative error for each MOS oscillator.

| OSCILLATOR                                                   | 1       | 2       | 3       |

|--------------------------------------------------------------|---------|---------|---------|

| $R_{\mathrm{s}}\left(\Omega\right)$                          | 387     | 79.0    | 5.14    |

| $R_{ m p}~({ m k}\Omega)$                                    | 1.07    | 1.07    | 0.607   |

| $L_{\mathrm{eq}}\left(\mathrm{nH} ight)$                     | 54.30   | 48.26   | 12.34   |

| $C_{\rm p}$ (fF)                                             | 44.74   | 45.48   | 83.00   |

| $C_{\mathrm{XCP}}\left(\mathbf{fF}\right)$                   | 258.99  | 262.34  | 244.18  |

| $C_{ m OUT_T}({ m fF})$                                      | 303.73  | 307.82  | 327.18  |

| $R_{	ext{XCP}}\left(\Omega ight)$                            | -399    | -403    | -545    |

| $f_{ m OSC_{aL}}\left( { m Hz}  ight)$                       | 1.239 G | 1.306 G | 2.505 G |

| Relative error $( f_{OSC_{aL}} - f_{OSC_{S}} /f_{OSC_{aL}})$ | 0.27    | 0.025   | 0.17    |

### 4.2.3 Temperature sensibility analysis

The oscillators' power consumption did not present significant variations across the temperature range, especially the oscillator 3. For a temperature of -40 °C, the oscillators 1 and 2 dissipated around 6.3 % and 3.2 % more power than at 27 °C and at 85 °C both oscillators dissipated around 2.5 % less. The oscillator 3 power consumption variation was less than 1.3 % in entire temperature range.

The decrease power consumption with temperature can be explained by the decrease of the mobility with the temperature increase [22], which, consequently, decreases  $I_{DS}$ , as stated in (2.2) and (2.3). So, as power consumption is given by the product of voltage and current, and voltage is constant (and equal to  $V_{DD}$ ) and current decreases, thus power consumption decreases.

The  $V_{pp}$  showed two types of tendencies:  $V_{pp}$  decreased when temperature increased, which is visible in oscillators 1 and 3; and the opposite tendency was found in oscillator 2 – the increase of  $V_{pp}$  with temperature decrease. Ultimately,  $V_{pp}$  is given by (4.22), combining (4.2) and (4.20).

$$Max(V_{\text{OUT}^{+,-}}) - Min(V_{\text{OUT}^{+,-}}) = \left(Max(r_{\text{ON}_{1,2}}) \cdot Min(I_{\text{OUT}_{1,2}}) - Min(r_{\text{ON}_{1,2}}) \cdot Max(I_{\text{OUT}_{1,2}})\right)$$

(4.22)

To confirm the results obtained in Figure 12 c),  $r_{\rm ON2}$  and  $I_{\rm OUT2}$  were simulated and extracted. The maximum and the minimum of these variables were used to calculate  $V_{\rm pp}$  through (4.21) for each one of the three oscillators. The results were plotted into a temperature sweep, as shown in Figure 14. Peak-to-peak variation of  $I_{\rm OUT2}$  decreases with temperature, as expected due to lower mobility of the semiconductor, for all oscillators. Peak-to-peak  $r_{\rm ON2}$  of oscillators 1 and 3 decreases with the temperature increase, so as both values decrease the  $V_{\rm pp}$  also decreases, as it is possible to observe in Figure 12 c) and Figure 14 a) and c). However,

Figure 12 - Temperature sensibility for each MOS oscillator. a) oscillation frequency; b) power consumption; c) output peak-to-peak voltage.

peak-to-peak  $r_{\rm ON2}$  of oscillator 2 increases with temperature increase, which translates to an increase of  $V_{\rm pp}$  with temperature. The  $r_{\rm ON}$  of transitor  $M_2$  is affected by the transistor  $M_{\rm aL2}$ . This latter transistor presents a wider W in oscillator 2, when comparing the same transistor in oscillators 1 and 3. This behavioral difference is associated with the model/sub model utilized in the simulation (BSIM3v3), since the equations are W and  $L_{\rm CH}$  dependent [23].

Figure 13 -  $C_{OUTT}$ ,  $L_{eq}$  and  $f_{OSCaL}$  versus of temperature, being blue, red, and green lines, respectively: a) Oscillator 1; b) Oscillator 2; c) Oscillator 3.

Figure 14 - Maximum and minimum of  $I_{DS2}$  (red curve) and  $r_{ON2}$  (blue curve) in function of temperature, being the maximum the solid line and minimum the dash line.  $V_{pp}$  obtained by (4.21) – dash green line – and the simulated  $V_{pp}$  in function of temperature – solid green line. a) Oscillator 1; b) Oscillator 2; c) Oscillator 3.

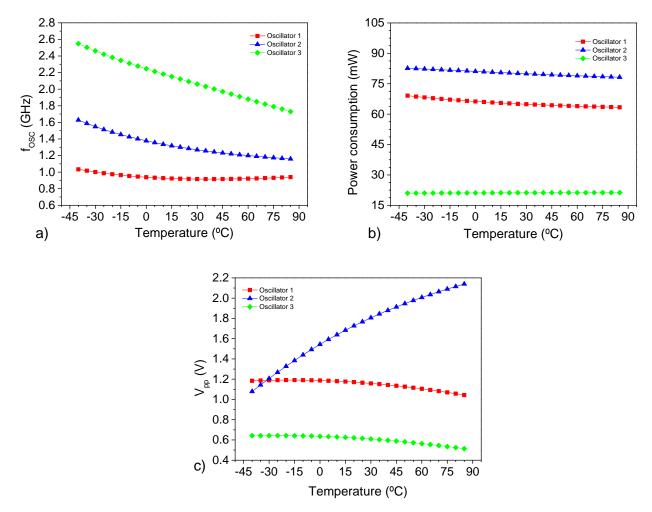

### 4.2.4 Phase noise simulation

Next, a phase noise analysis was performed following the procedure described in section 3.2.1.1. The phase noise is a fundamental design specification for oscillators in RF applications. Phase noise quantifies the spread of the oscillator signal power to nearby frequencies [24]. It is measured at the power of the 1-Hz bandwidth of the spectrum at a given offset. The power is normalized by the carrier power. Phase noise is usually indicated in dBc/Hz at a given offset from the oscillator fundamental frequency or its harmonics[16].

The phase noises at 1 MHz offset from the fundamental frequency for each oscillator are presented in Figure 15 and the results are presented Table 5. The phase noise is inversely proportional to the Q-factor of inductive elements [16], [25]. Oscillator 2 presented the lowest phase noise, however, the Q-factors at  $f_{\rm OSC_S}$  – (4.7) – of Table 5 do not corroborate with these results, which could be a direct consequence of the larger error of RLC EC values of oscillators 1 and 3, allowing to conclude that Q-factors are lower than estimated. Nevertheless, it is not possible to affirm with certain, so, further study is necessary to fully understand these different behaviors.

Figure 15 - Phase noise at 1 MHz offset from the fundamental frequency for each MOS oscillator: a) Oscillator 1; Oscillator 2; c) Oscillator 3.

Table 5 - Phase noise at 1 MHz of offset for each MOS oscillator, and respective Q-factor at foscs.

| Oscillator                          | 1      | 2      | 3      |

|-------------------------------------|--------|--------|--------|

| Phase noise @ 1 MHz offset (dBc/Hz) | -96.73 | -104.7 | -92.86 |